#### **Computer Science Basics**

Lecturer: Serge Klimenkov v.1.14.e from 08.06.2018

## How computer works?

1

# Analog Computers

Only suitable for a particular class of tasks

- High performance

- Lower comutational errors

# Analog Computers

- High accuracy of data representation

- Relatively large dimensions

## Digital Computers

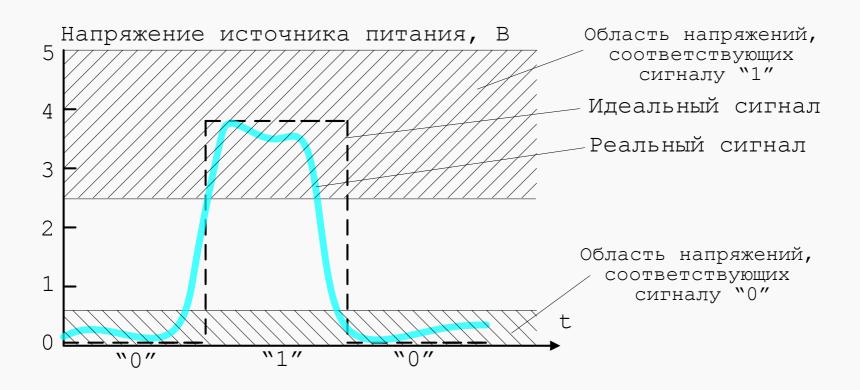

All information is represented using only two discrete values — 0 and 1

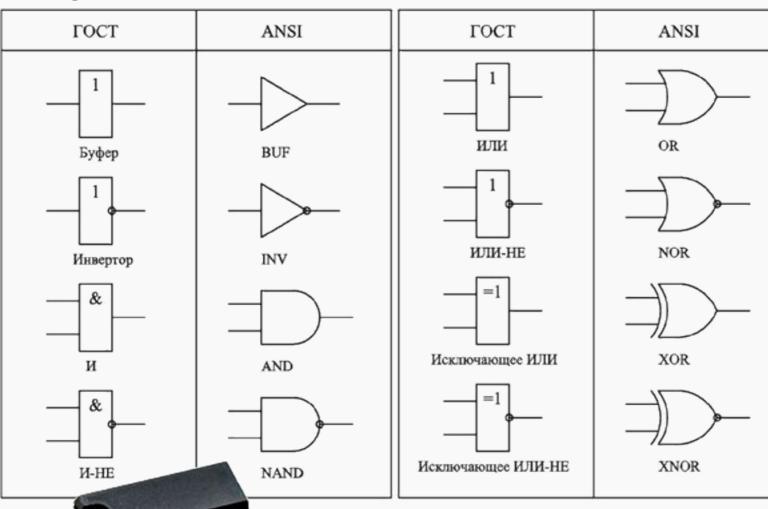

#### Logic elements:

| AND |    |     |   |  |  |  |

|-----|----|-----|---|--|--|--|

| X1  | X2 | Y   |   |  |  |  |

| 0   | 0  | 0   | 1 |  |  |  |

| 0   | 1  | 0   | 1 |  |  |  |

| 1   | 0  | 0 0 |   |  |  |  |

| 1   | 1  | 1   | 0 |  |  |  |

| OR |                      |   |   |  |  |  |  |  |

|----|----------------------|---|---|--|--|--|--|--|

| X1 | (1 X2 Y \overline{Y} |   |   |  |  |  |  |  |

| 0  | 0                    | 0 | 1 |  |  |  |  |  |

| 0  | 1                    | 1 | 0 |  |  |  |  |  |

| 1  | 0                    | 1 | 0 |  |  |  |  |  |

| 1  | 1                    | 1 | 0 |  |  |  |  |  |

| XOR |           |   |   |  |  |  |  |

|-----|-----------|---|---|--|--|--|--|

| X1  | X1 X2 Y Y |   |   |  |  |  |  |

| 0   | 0         | 0 | 1 |  |  |  |  |

| 0   | 1         | 1 | 0 |  |  |  |  |

| 1   | 0         | 1 | 0 |  |  |  |  |

| 1   | 1         | 1 | 1 |  |  |  |  |

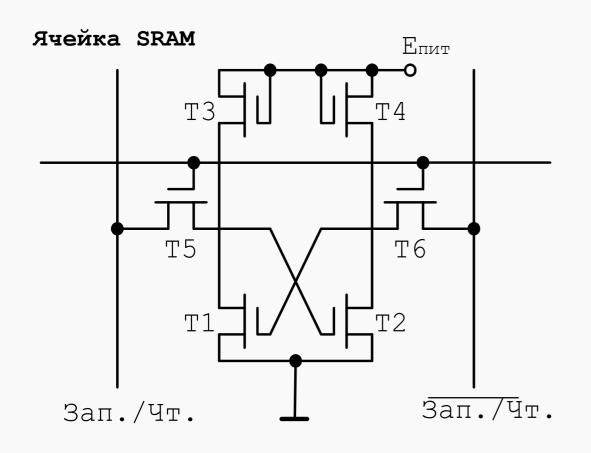

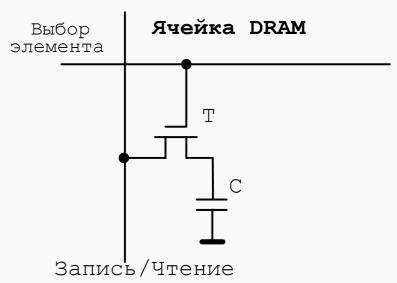

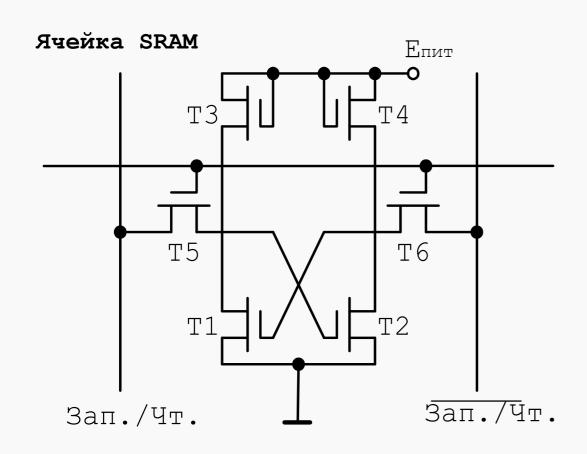

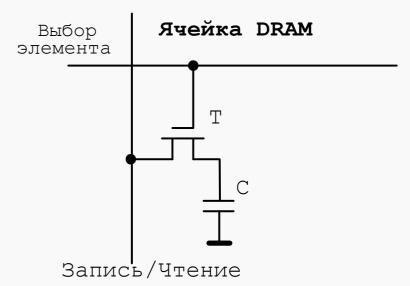

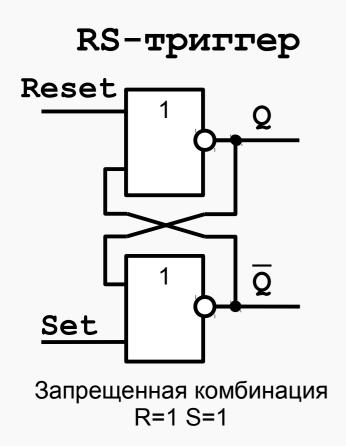

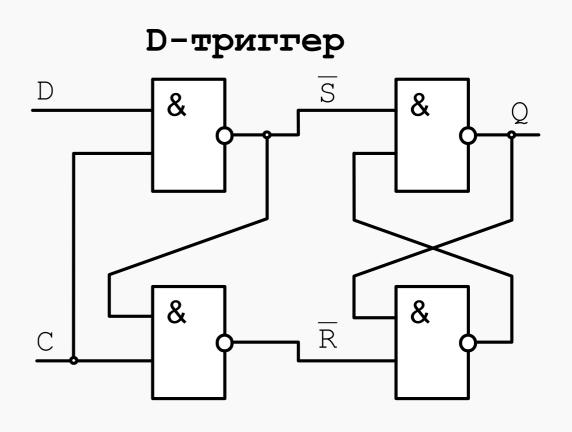

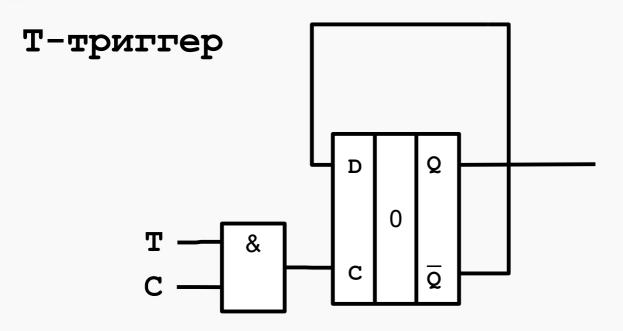

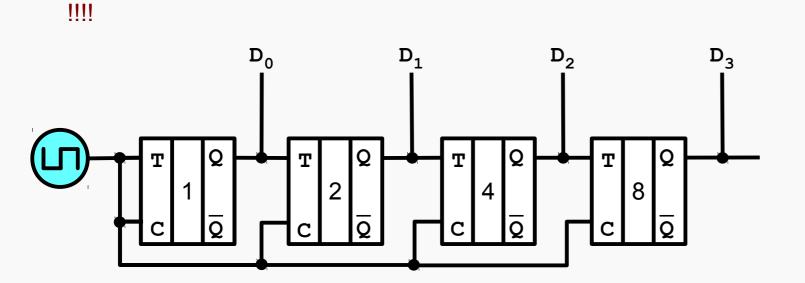

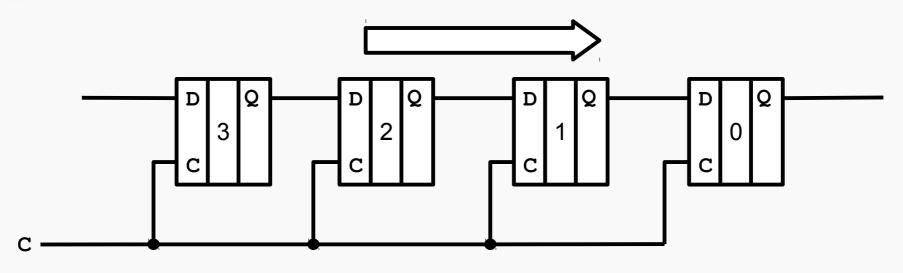

Memory units (DRAM/SRAM)

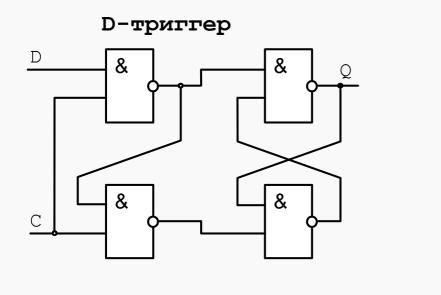

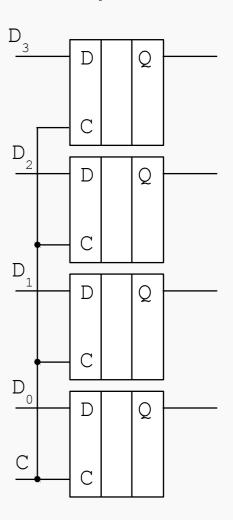

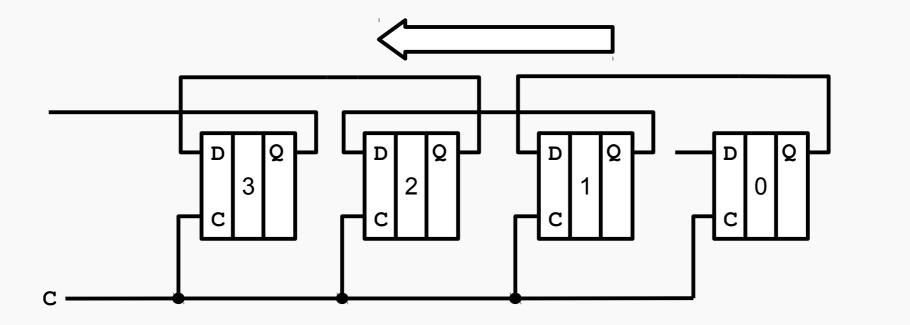

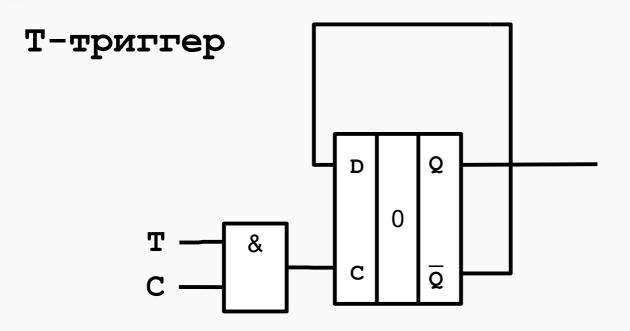

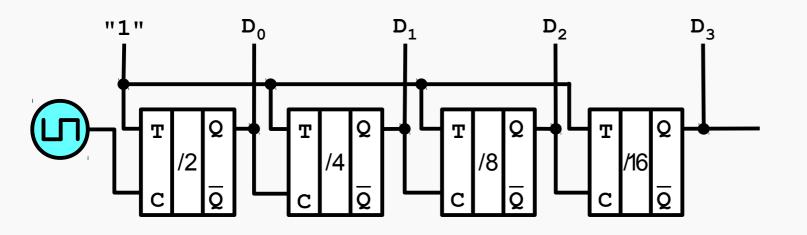

Memory units (flip-flop circuits, registers)

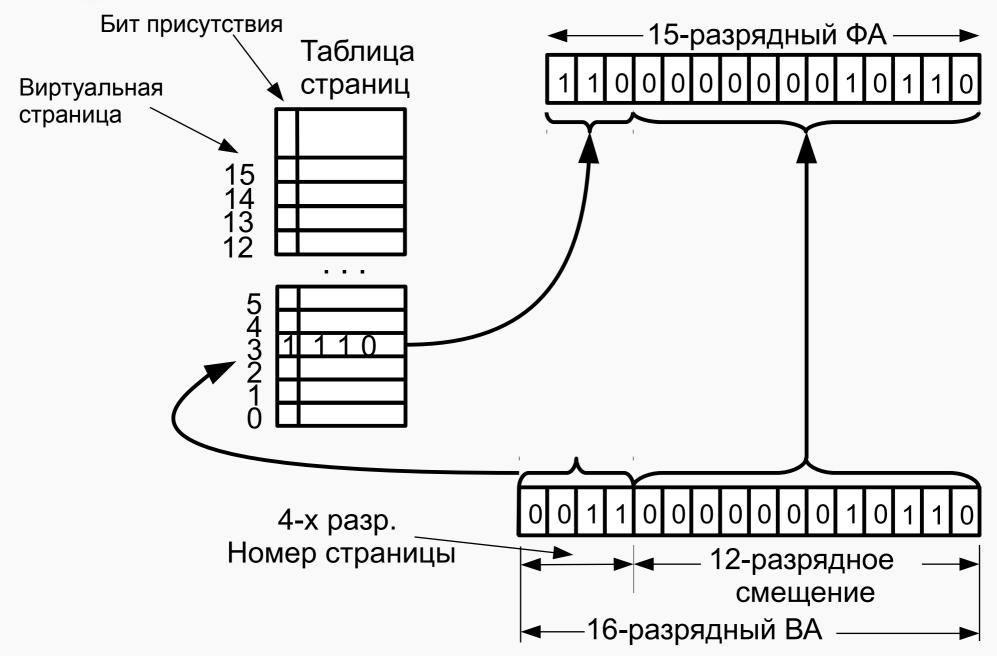

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

0

1

1

0

0

0

0

0

0

0

1

0

1

1

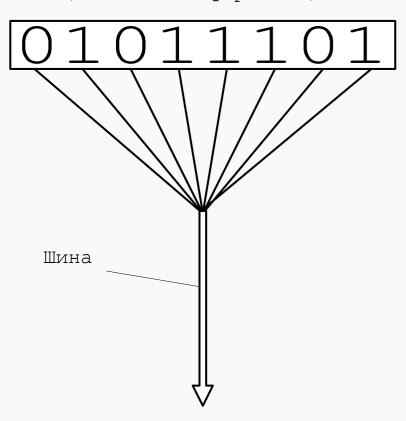

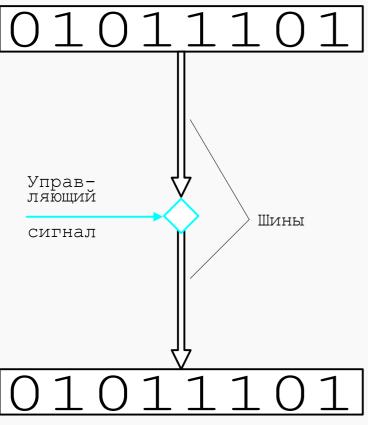

#### Cables, buses

Регистр (источник информации)

#### Logic gates:

Регистр (источник информации)

Регистр (приемник информации)

| Logic gate (AND) |   |   |  |  |  |  |

|------------------|---|---|--|--|--|--|

| Contr. In Out    |   |   |  |  |  |  |

| 0                | 0 | 0 |  |  |  |  |

| 0                | 1 | 0 |  |  |  |  |

| 1                | 0 | 0 |  |  |  |  |

| 1                | 1 | 1 |  |  |  |  |

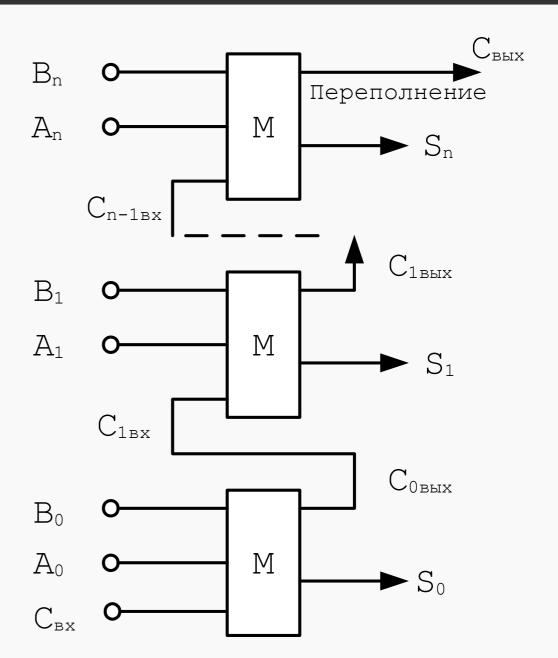

# Adders (part of the ALU)

| SUM |     |    |      |    |  |  |  |

|-----|-----|----|------|----|--|--|--|

| Sin | Ai  | Bi | Sout | Si |  |  |  |

| 0   | 0   | 0  | 0    | 0  |  |  |  |

| 0   | 0 0 |    | 0    | 1  |  |  |  |

| 0   | 1   | 0  | 0    | 1  |  |  |  |

| 0   | 1   | 1  | 1    | 0  |  |  |  |

| 1   | 0   | 0  | 0    | 1  |  |  |  |

| 1   | 0   | 1  | 1    | 0  |  |  |  |

| 1   | 1   | 0  | 1    | 0  |  |  |  |

| 1   | 1   | 1  | 1    | 1  |  |  |  |

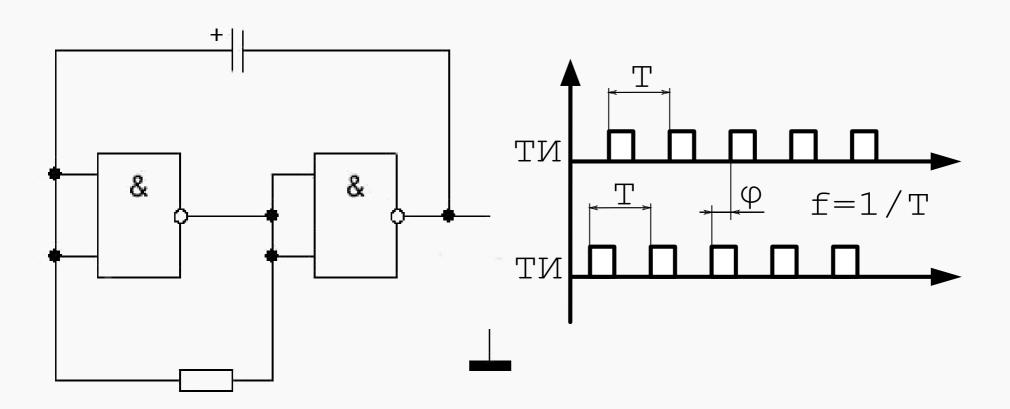

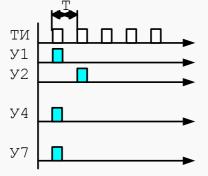

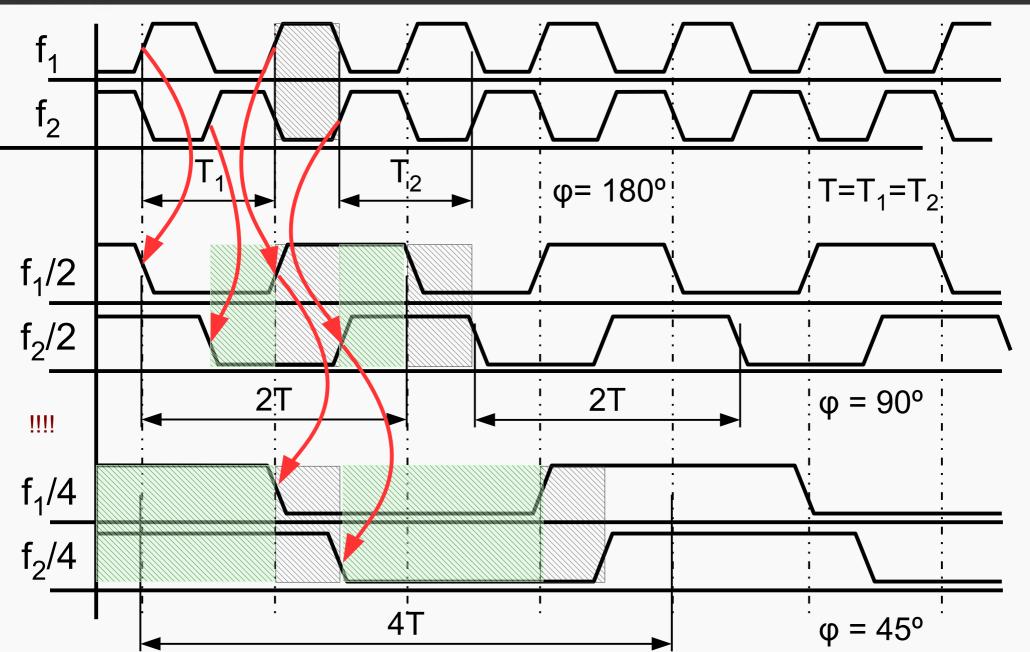

Clock generators

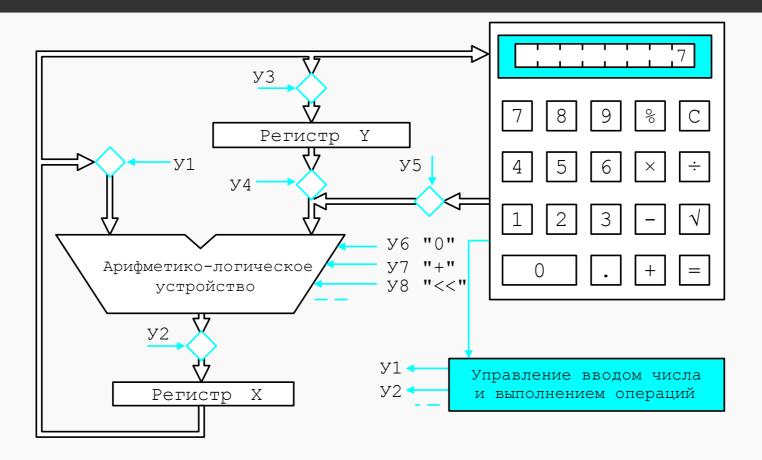

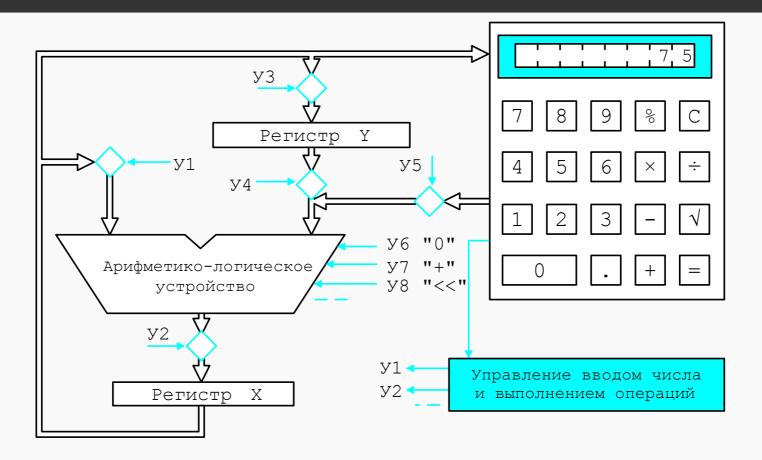

### The First Computer: Calculator (1)

#### Ввод первой цифры числа

- 1. (У3) Переслать содержимое регистра X в регистр Y

- 2. (У2, У6) Записать "0" в регистр Х

- 3. (У1, У5, У7) Сложить X (0) с цифрой с клавиатуры

- 4. (У2) Записать результат в Х

## The First Computer: Calculator (2)

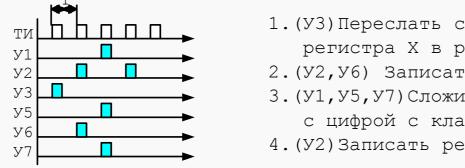

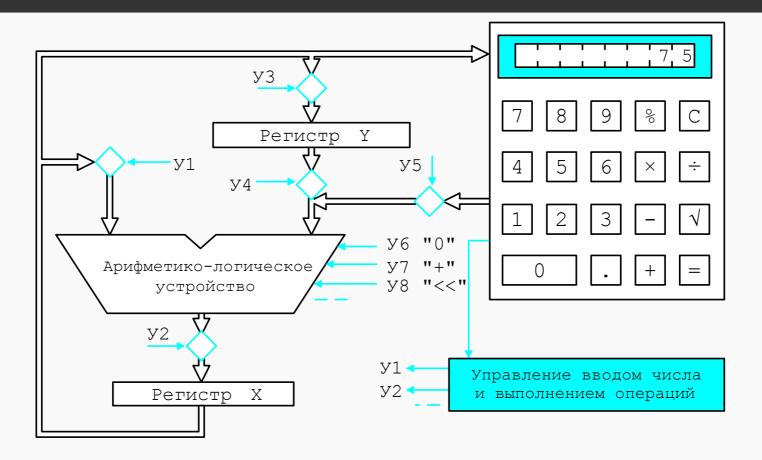

#### Ввод второй (и последующих) цифр числа

- 1. (У1, У8) Сдвинуть содержимое регистра X на 1 разряд (\*10)

- 2.(У2) Записать результат в регистр Х

- 3.(У1,У5,У7)Сложить X с цифрой с клавиатуры

- 4.(У2) Записать результат в Х

## The First Computer: Calculator (3)

#### Сложение регистра X и регистра Y

- 1. (У1, У4, У7) Сложить содержимое регистра X и регистра Y

- 2.(У2) Записать результат в регистр X

# Do you know, how to drive that thing?

- Tank, drive program, please

- Not yet.

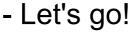

#### **UNIX-like OS**

2

# History

#### Modern Time

- System V

- Solaris, AIX, HPUX

- BSD

- Mac OS X

- NetBSD, FreeBSD, OpenBSD

- Linux

- RedHat, Ubuntu, SUSE

- Fedora, Debian, OpenSUSE, ArchLinux

- Gentoo

\_ ...

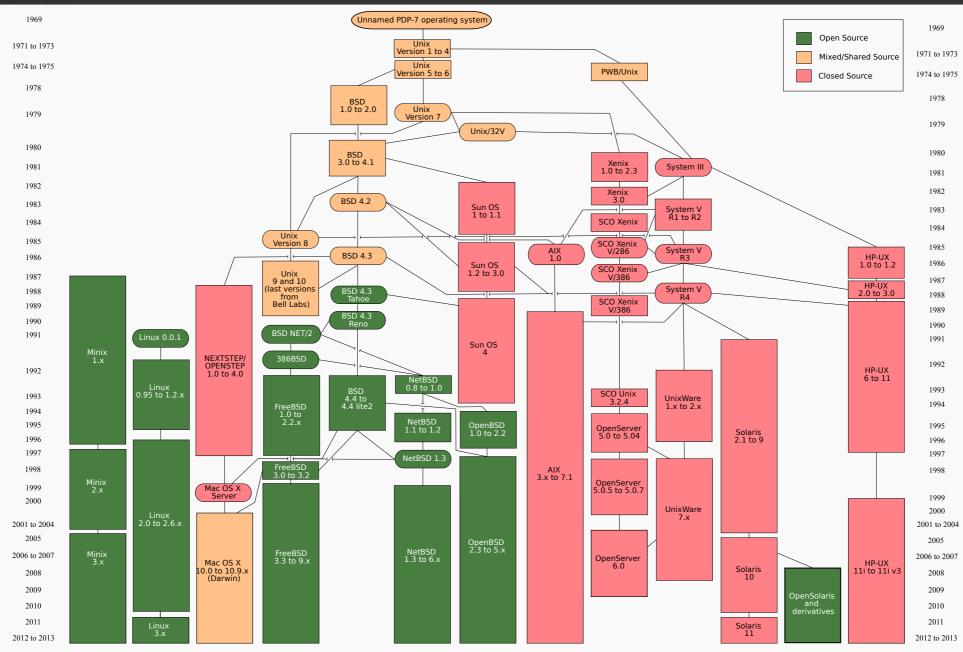

#### \*NIX Kernel

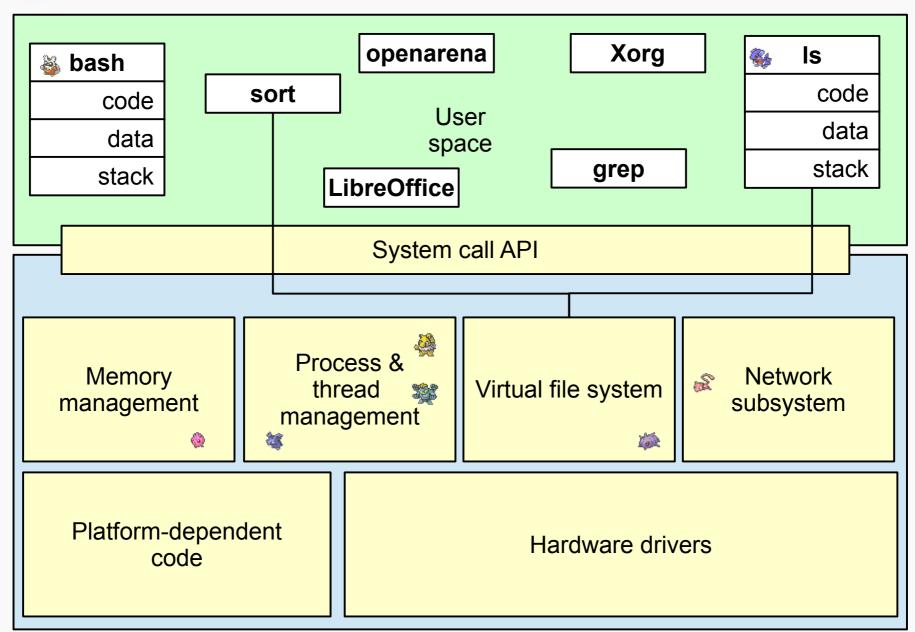

## File System

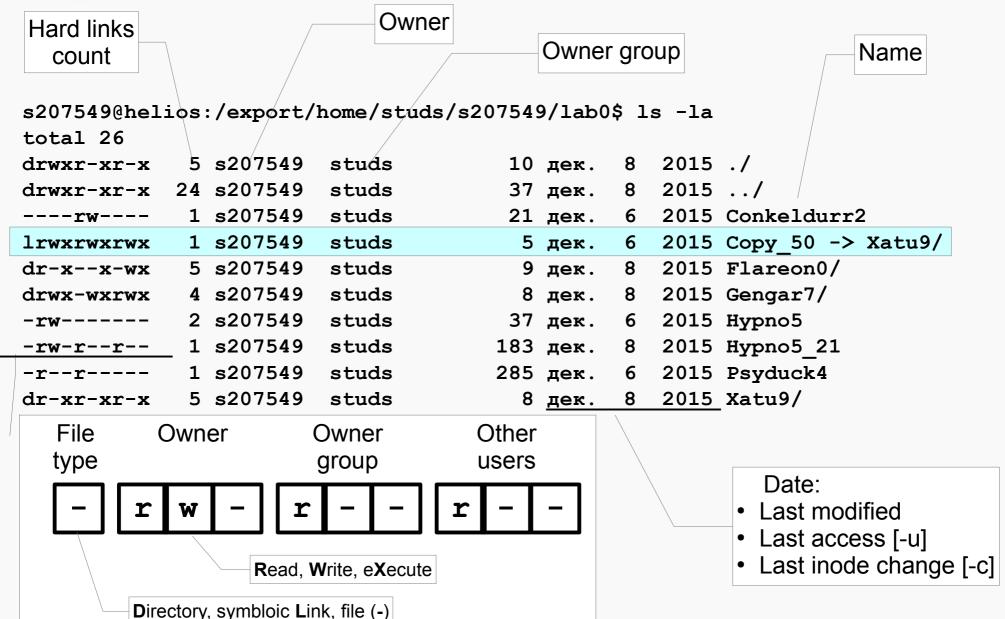

## File Access Rights

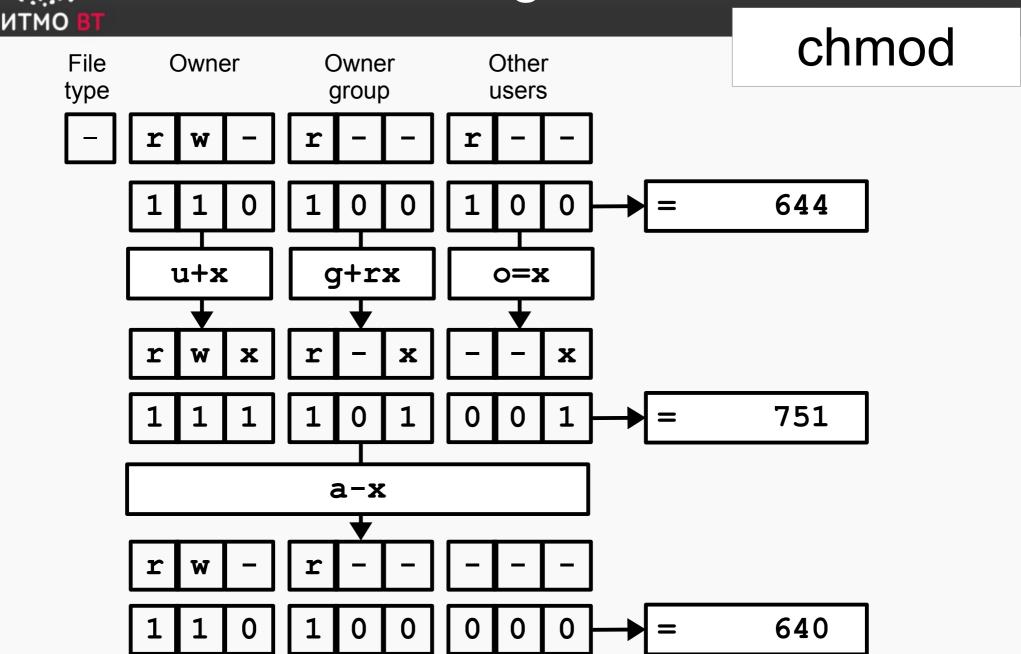

#### File Access Rights Administration

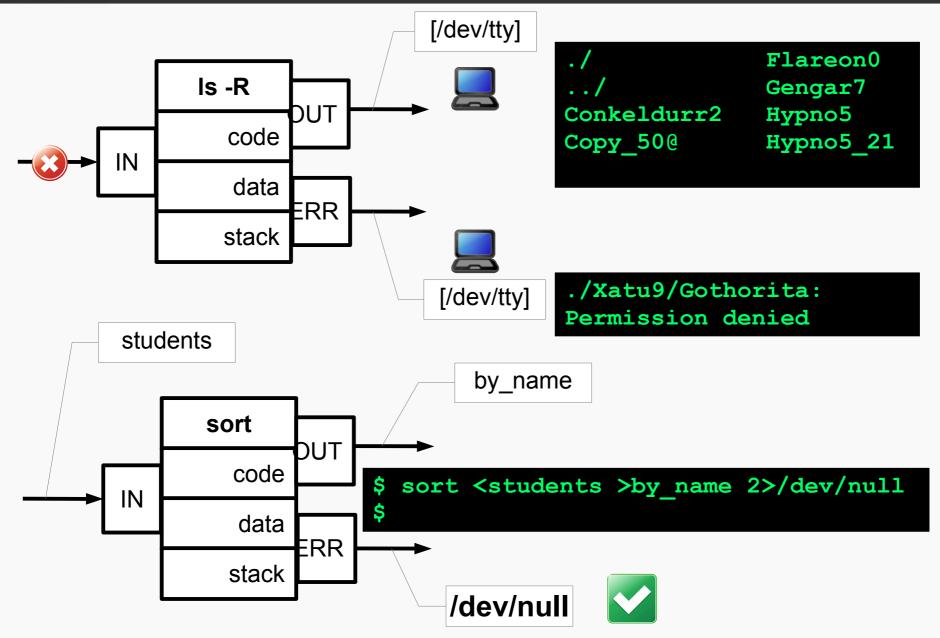

# stdin(0), stdout(1) & stderr(2) streams

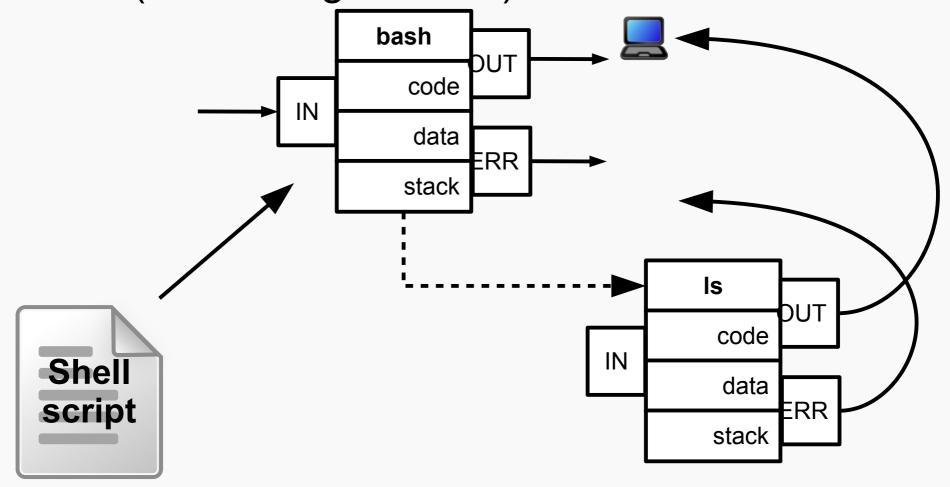

#### Shell

sh (Bourne shell) ksh (Korn shell) csh (C shell) bash (Bourne-again shell)

# stdin(0), stdout(1) & stderr(2) streams

- > file redirect stdout to file

- >> file add stdout to file

- 2> file redirect stderr to file

- 2>> file add stderr to file

- < file get stdin from file

- << EOF write all text from terminal until «EOF» symbol to stdin</li>

- 1s | sort redirect stdout of 1s command to stdin of sort command

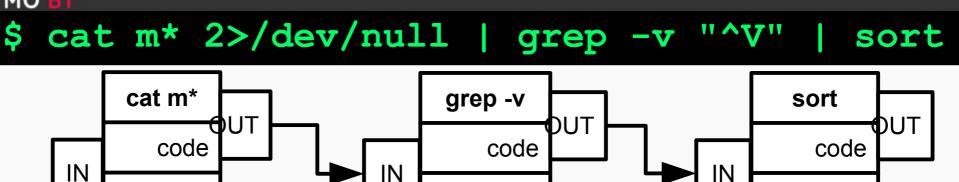

#### **Filters**

data

stack

ERR

/dev/null

message1

**H**RR

#### Vasya:

For meat was hard to come by

data

stack

Troll sat alone on his seat of stone And munched and mumbled a bare old bone For many a year he had gnawed it near For meat was hard to come by

#### message2 **Viktor:**

And munched and mumbled a bare old bone

message4

#### Vasya:

Troll sat alone on his seat of stone

#### Veronika:

For many a year he had gnawed it near

message3

data

stack

ERR

### Regular Expressions

#### messages

Vasya:

Troll sat alone on his seat of stone

Viktor:

And munched and mumbled a bare old bone Veronika:

For many a year he had gnawed it near Vasya:

For meat was hard to come by

- Any letter corresponds to itself

- ^ line start

- \$ end of line

- . any single letter

```

$ grep meat messages

For meat was hard to come by

$ grep "^V" messages

Vasya:

Viktor:

Veronika:

Vasya:

$ grep "a.e" messages

```

#### **Basic Commands**

| Command | Description                 |

|---------|-----------------------------|

| mkdir   | mkdir [-m mode] [-p] dir    |

| echo    | echo [string]               |

| cat     | cat [-n] [file] [-]         |

| touch   | touch [-am] file            |

| ls      | ls [options] [file/dir]     |

| pwd     | pwd                         |

| cd      | cd [argument]               |

| more    | more [file]                 |

| ср      | cp [options] SOURCE DEST    |

| rm      | rm [options] [file/dir]     |

| rmdir   | rmdir [dir]                 |

| m∨      | mv [-fi] SOURCE DEST        |

| head    | head [-num] [file]          |

| tail    | tail [-/+num] [-bcl] [file] |

| sort    | sort [-unr] [-k num] [file] |

| grep    | grep [-v] regexp [file]     |

| WC      | wc [-c   -m ] [-lw] [file]  |

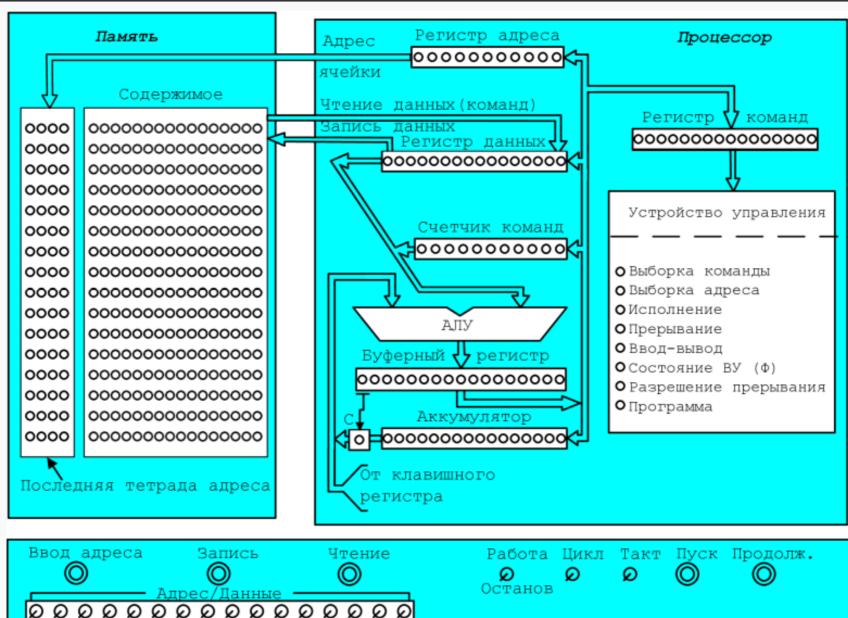

# Acquaintance with the Basic Computer

3

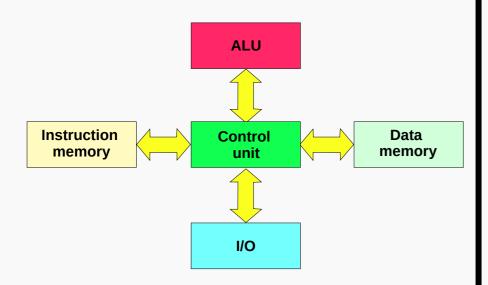

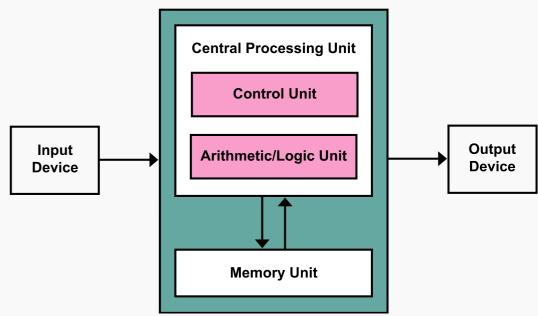

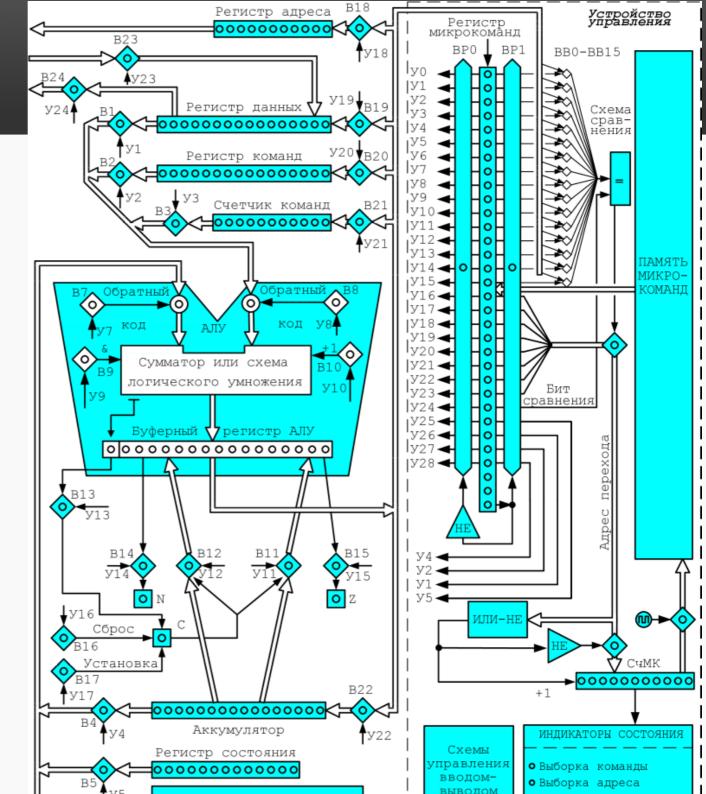

## Computer Architecture

#### Harvard Architecture

#### Von Neumann Architecture

# Basic Computer (BComp)

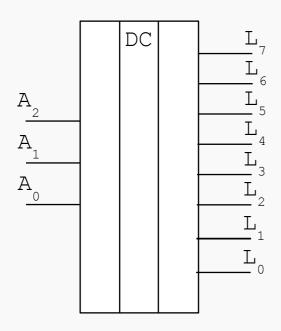

## Decoder

| Адрес          |                       |                | String |                |                |                |                |                |                |                |                |

|----------------|-----------------------|----------------|--------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| A <sub>2</sub> | <b>A</b> <sub>1</sub> | A <sub>0</sub> |        | L <sub>7</sub> | L <sub>6</sub> | L <sub>5</sub> | L <sub>4</sub> | L <sub>3</sub> | L <sub>2</sub> | L <sub>1</sub> | L <sub>o</sub> |

| 0              | 0                     | 0              |        | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 1              |

| 0              | 0                     | 1              |        | 0              | 0              | 0              | 0              | 0              | 0              | 1              | 0              |

| 0              | 1                     | 0              |        | 0              | 0              | 0              | 0              | 0              | 1              | 0              | 0              |

| 0              | 1                     | 1              |        | 0              | 0              | 0              | 0              | 1              | 0              | 0              | 0              |

| 1              | 0                     | 0              |        | 0              | 0              | 0              | 1              | 0              | 0              | 0              | 0              |

| 1              | 0                     | 1              |        | 0              | 0              | 1              | 0              | 0              | 0              | 0              | 0              |

| 1              | 1                     | 0              |        | 0              | 1              | 0              | 0              | 0              | 0              | 0              | 0              |

| 1              | 1                     | 1              |        | 1              | 0              | 0              | 0              | 0              | 0              | 0              | 0              |

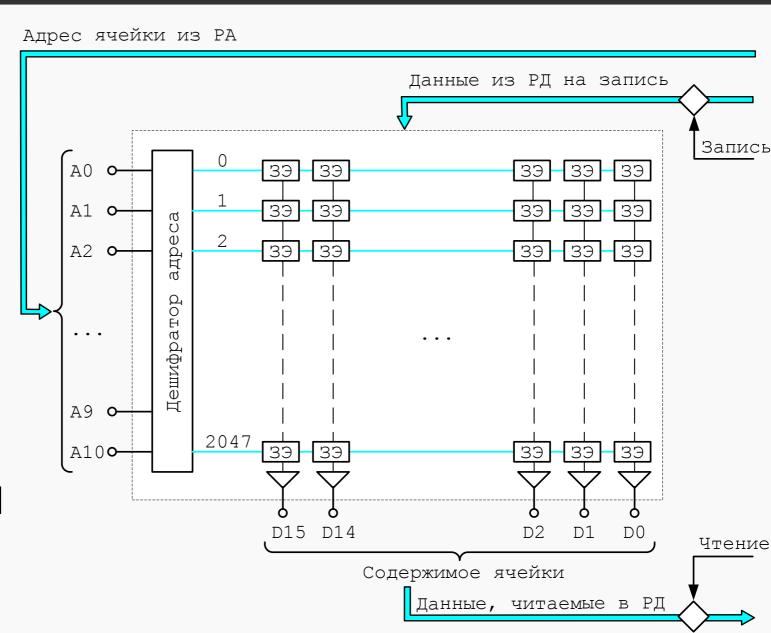

### BComp Addressable Memory

- A total of 2048 16-bit cells

- Cells 008-00F are index cells

- Cells 000 & 001 are used for interrupts

#### **ALU**

#### Control Unit

#### Instruction cycle

- ► 1. Instruction fetch cycle

- → 2. Address fetch cycle

- → 3. Execution cycle

- → 4. Interruption cycle

#### **Operational console cycles**

- → Address input

- → Read

- → Write

- ➤ Start

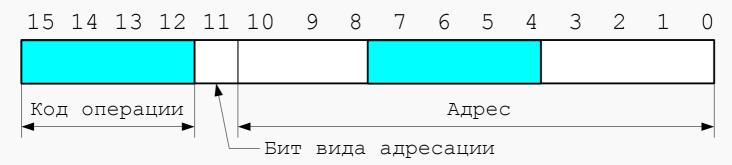

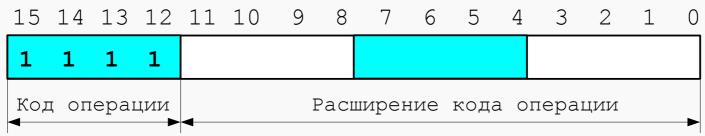

### **Instruction Formats**

#### Адресные команды

#### Безадресные команды

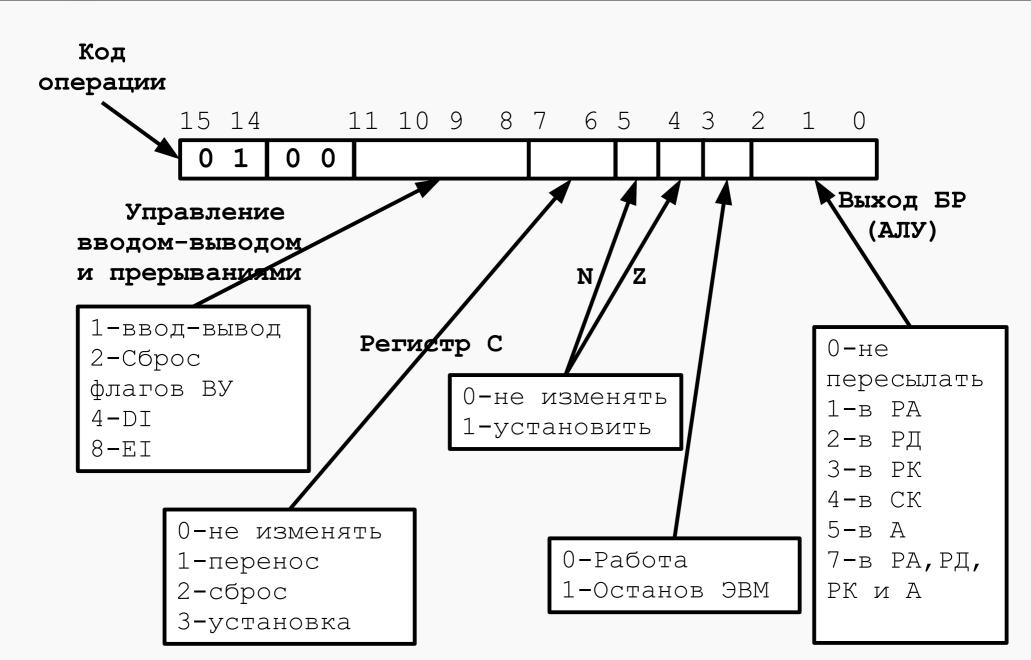

#### Команды ввода-вывода

### Address Instructions

| Name                   | Mnemonic name | Code | Description                                                             |

|------------------------|---------------|------|-------------------------------------------------------------------------|

| Conjunction            | AND M         | 1XXX | (M) & (A) → A                                                           |

| Move                   | MOV M         | 3XXX | (A) <b>→</b> M                                                          |

| Addition               | ADD M         | 4XXX | (M) + (A) → A                                                           |

| Addition with carry    | ADC M         | 5XXX | $(M) + (A) + (C) \rightarrow A$                                         |

| Substraction           | SUB M         | 6XXX | (A) − (M) → A                                                           |

| Branch if carry is set | BCS M         | 8XXX | If (C) = 1, then M → IP                                                 |

| Branch if plus         | BPL M         | 9XXX | If (N)= 0, then M → IP                                                  |

| Branch if minus        | BMI M         | AXXX | If (N) = 1, then M → IP                                                 |

| Branch if zero         | BEQ M         | BXXX | If $(Z) = 1$ , if $M \rightarrow IP$                                    |

| Unconditional branch   | BR M          | CXXX | M → IP                                                                  |

| Increment and skip     | ISZ M         | 0XXX | $M + 1 \rightarrow M$ , if $(M) \ge 0$ , then $(IP) + 1 \rightarrow IP$ |

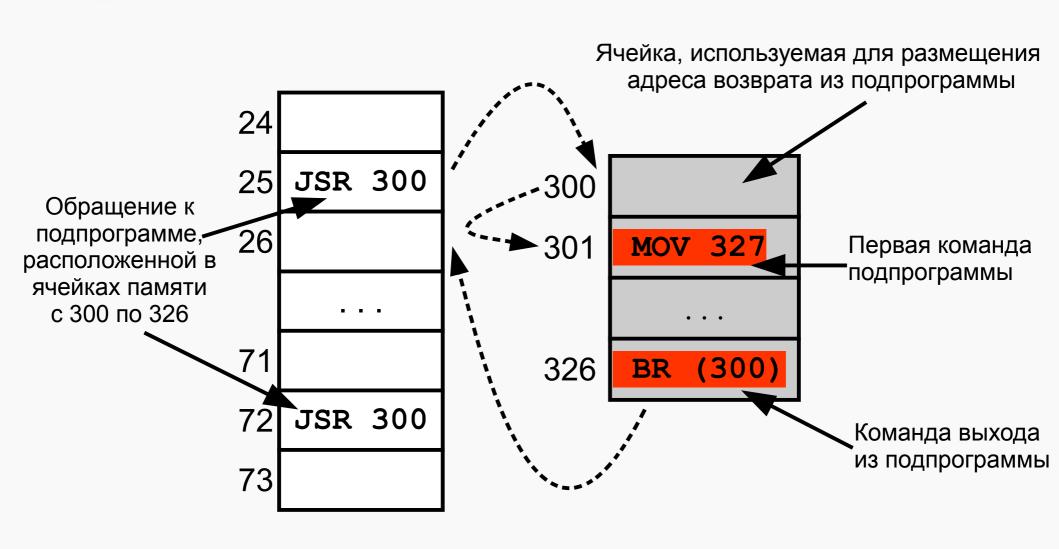

| Subprogram call        | JSR M         | 2XXX | (IP) → M, M + 1 → IP                                                    |

### No-address Instructions

| Name                           | Mnemonic name | Code | Description                                                           |

|--------------------------------|---------------|------|-----------------------------------------------------------------------|

| Clear accumulator register     | CLA           | F200 | 0 <b>→</b> A                                                          |

| Clear carry register           | CLC           | F300 | 0 <b>→</b> C                                                          |

| Invert accumulator register    | CMA           | F400 | (!A) → A                                                              |

| Invert carry register          | CMC           | F500 | (!C) → C                                                              |

| Left cyclic shift by 1 bit     | ROL           | F600 | A & C content moves left, A(15) $\rightarrow$ C, C $\rightarrow$ A(0) |

| Right cyclic shift by 1 bit    | ROR           | F700 | A & C content moves right, A(0) → C, C → A(15)                        |

| Increment accumulator register | INC           | F800 | (A) + 1 → A                                                           |

| Decrement accumulator register | DEC           | F900 | (A) − 1 → A                                                           |

| Halt                           | HLT           | F000 |                                                                       |

| No operation                   | NOP           | F100 |                                                                       |

| Enable interruptions           | EI            | FA00 |                                                                       |

| Disable interruptions          | DI            | FB00 |                                                                       |

## I/O Instructions

| Name       | Mnemonic name | Code | Description                                |

|------------|---------------|------|--------------------------------------------|

| Clear flag | CLF B         | E0XX | 0 → device flag                            |

| Check flag | TSF B         | E1XX | If (device flag B) = 1, then (IP) + 1 → IP |

| Input      | IN B          | E2XX | (B) → A                                    |

| Output     | OUT B         | E3XX | (A) → B                                    |

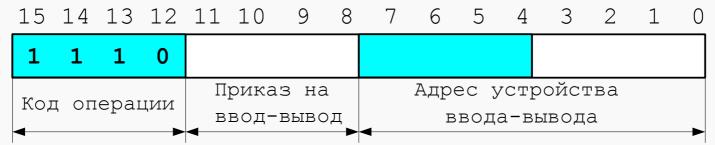

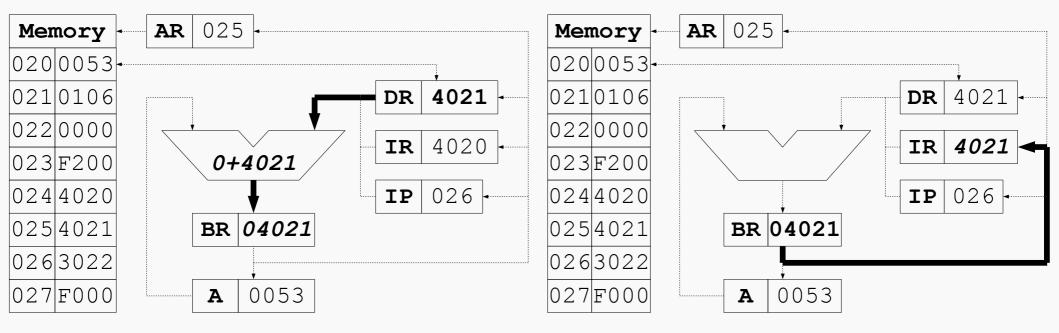

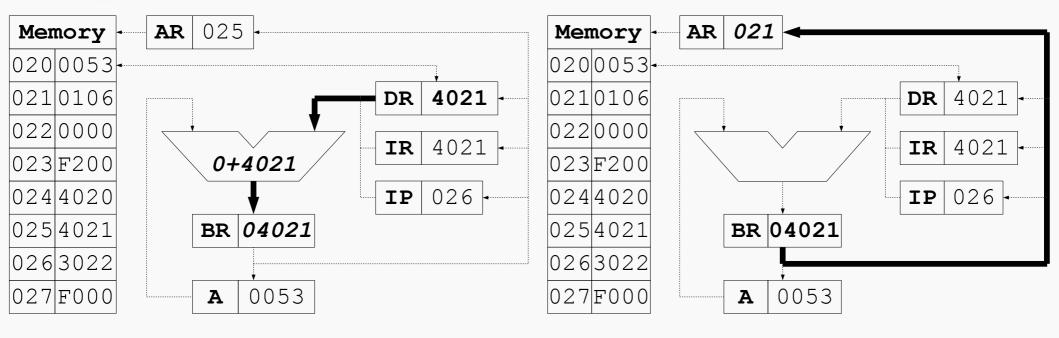

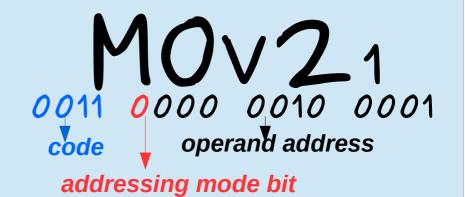

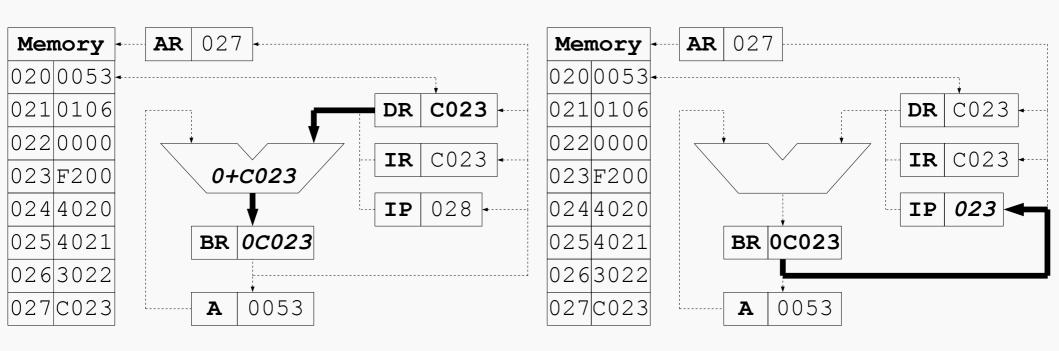

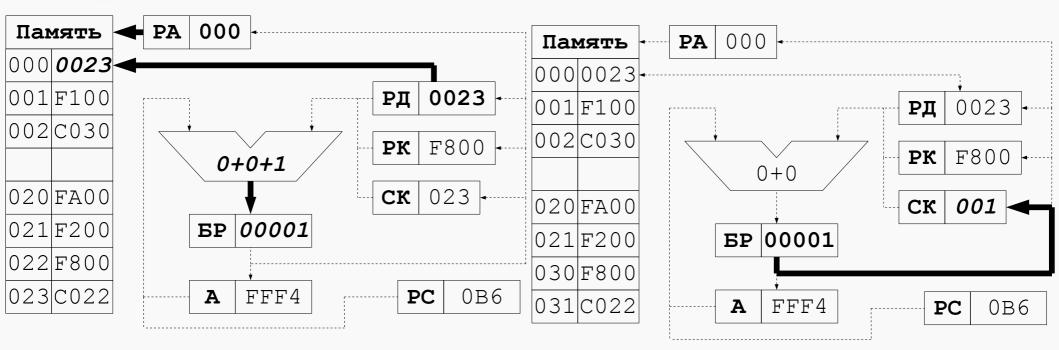

# Instruction Fetch Cycle: ADD 21

1) Transfer IP content to BR through ALU.

2) Transfer 11 lower bits of BR content to AR.

# Instruction Fetch Cycle: ADD 21

- 3) Fetch instruction code by address from AR (025) and save it to DR. At the same time increment IP content and save it to BR.

- 4) Transfer 11 lower bits of BR content to IP.

# Instruction Fetch Cycle: ADD 21

- 5) Save DR content to BR through the right input of the ALU.

- 6) Transfer 16 lower bits of the BR content to IR.

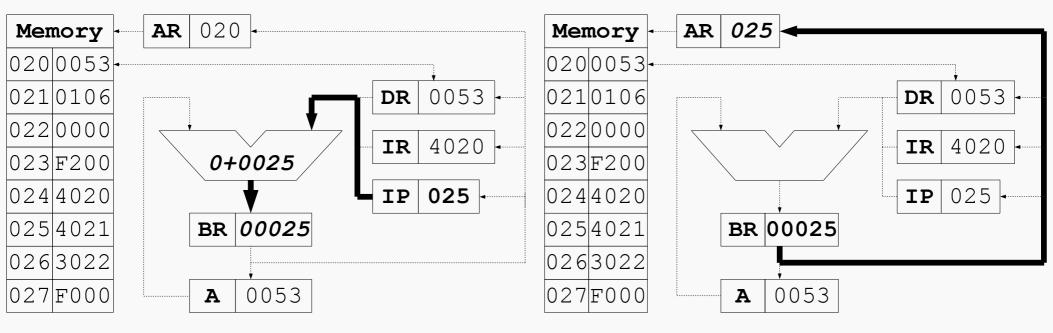

# Execution Cycle of the Direct Addressing Instruction: ADD 21

- 1) Save DR content to BR through the right input of the ALU.

- 2) Transfer 11 lower bits of the BR content to AR.

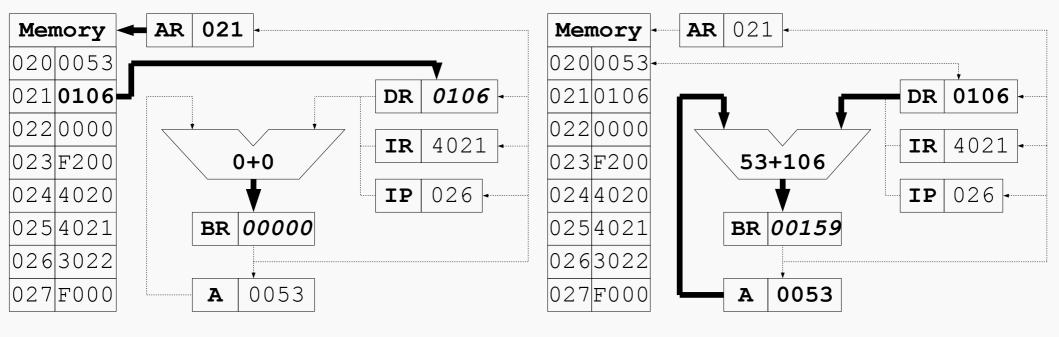

# Execution Cycle of the Direct Addressing Instruction: ADD 21

3) Save content of the memory cell 021 (addition operand) to DR. **Reset BR!**

4) Perform addition of the BR content (on the right input of the ALU) with the A content (on the left input of the ALU) and save it to BR.

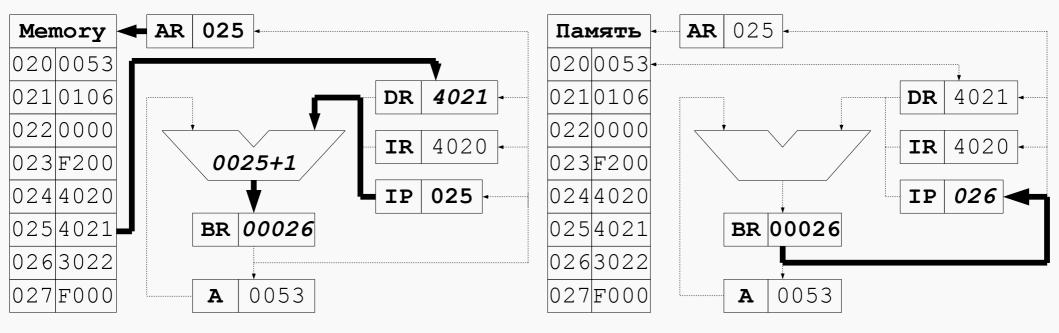

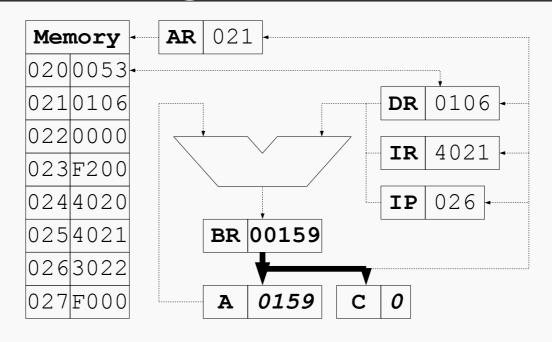

# Execution Cycle of the Direct Addressing Instruction: ADD 21

5) Save lower 16 bits (from 0 to 15th) of the BR content to A, save 16th bit of the BR content to C (carry) bit of the SR. Reset N & Z result attributes.

# Representation of the Information

4

## Representation Area

3021 — what does it mean?

# Representation Area

12321

### **Allowed Values**

- Are determined by the representation area.

- Examples:

- No-address instructions of the BComp

- Logical values

True, False

F000, F100, F200, F300, F400, F500, F600, F700, F800, F900, FA00, FB00

- Integers < 65535

1,2,3,4,5,6,7,.....65531,65532,65533,65534,65535

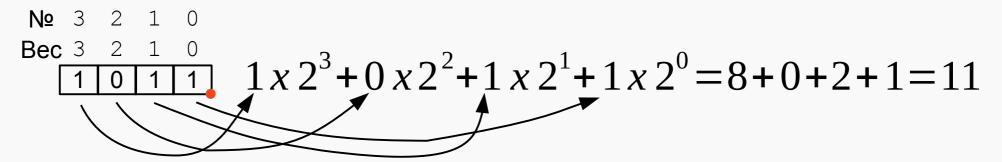

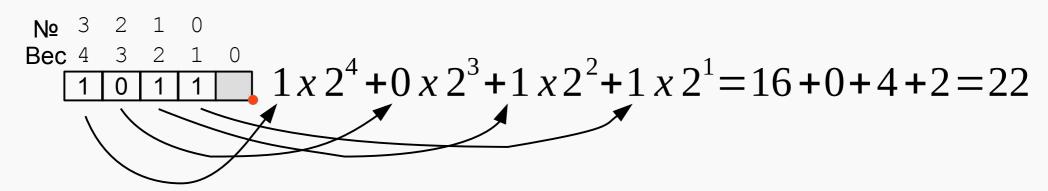

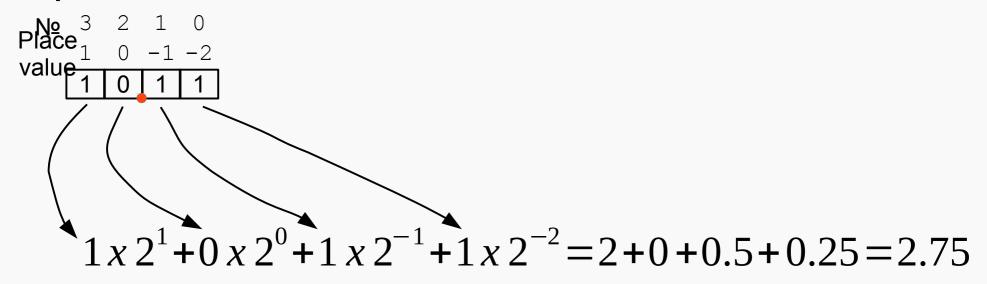

# Numbers Representation: Fixed Point

- Integers: binary radix point is on the fixed position after bit 0, all bits have a positive place value:

- 1) Bit number equals its place value

2) Bit place value = bit number +1

# Numbers Representation: Fixed Point

Real numbers: binary radix point is on the fixed position after bit 2, lower two bits have a negative place values:

Real numbers: moving the decimal radix point causes the scale change:

# Unsigned Integers Representation

- Number of bits in the bit grid of the computer defines its allowable range:

- Minimum 4-bit unsigned number:

$$0 \times 2^{3} + 0 \times 2^{2} + 0 \times 2^{1} + 0 \times 2^{0} = 0$$

- Maximum 4-bit unsigned number:

$$1x2^{3}+1x2^{2}+1x2^{1}+1x2^{0}=15=2^{4}-1$$

- Range:

$$0 \le X \le 2^4 - 1$$

Range for 16-bit unsigned numbers:

$$0 \le X \le 2^{16} - 1 = 65535$$

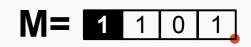

# Signed Integers Representation

- One bit specifies the sign of the number.

For example, «0» means «+» and «1» means «-».

- Ones' complement:

$$-7 = -(2^3 - 1) \le X \le 2^3 - 1 = 7$$

Double zero!

- Two's complement:

$$M = b^n - K$$

M — complement of the K (10-3=7)!

b — numeral system's base

*n* — number of bits

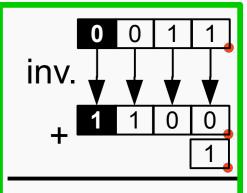

# Signed Integers: Two's Complement

$$M = b^{n} - K = ((b^{n} - 1) - K) + 1$$

| One's                            | Two's complement              |                     |                     |      |      |      |  |

|----------------------------------|-------------------------------|---------------------|---------------------|------|------|------|--|

| compl. for<br>5-digit<br>numbers | 5-digit<br>decimal<br>numbers | 4-digit hex numbers | I DENIT DIDARY DIIR |      | bers |      |  |

| -50000                           | 50000                         |                     |                     |      |      |      |  |

| -49999                           | 50001                         |                     |                     |      |      |      |  |

| -32768                           | 67232                         | 8000                | 1000                | 0000 | 0000 | 0000 |  |

| -32767                           | 67233                         | 8001                | 1000                | 0000 | 0000 | 0001 |  |

| -2                               | 99998                         | FFFE                | 1111                | 1111 | 1111 | 1110 |  |

| -1                               | 99999                         | FFFF                | 1111                | 1111 | 1111 | 1111 |  |

| 0                                | 00000                         | 0000                | 0000                | 0000 | 0000 | 0000 |  |

| 1                                | 00001                         | 0001                | 0000                | 0000 | 0000 | 0001 |  |

| 32767                            | 32767                         | 7FFF                | 0111                | 1111 | 1111 | 1111 |  |

| 49999                            | 49999                         |                     |                     |      |      |      |  |

|   | K=+3 |   |   |  |  |

|---|------|---|---|--|--|

| 3 | 2    | 1 | 0 |  |  |

| 0 | 0    | 1 | 1 |  |  |

$$M = b^{n} - K$$

$2^{4} - 3 = 13$

$1 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 1 \quad 1$

$$M = \begin{bmatrix} 1 & 1 & 0 & 1 \end{bmatrix}$$

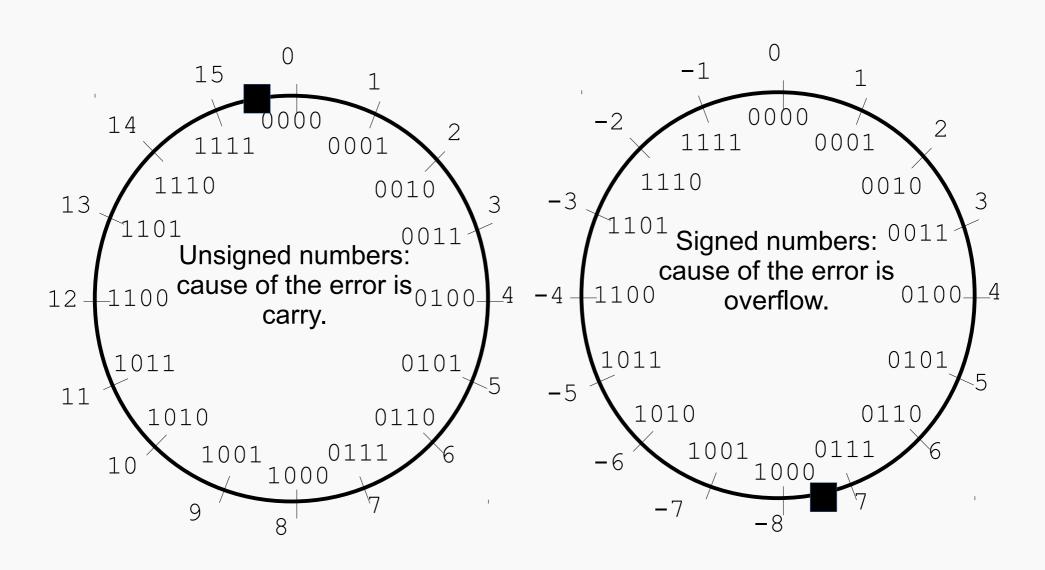

# Carry & Overflow

# Numbes Representation in BComp

| Bit grid representation | Unsigned numbers | Signed numbers     |

|-------------------------|------------------|--------------------|

| 0000 0000 0000 0000     | 0                | 0                  |

| 0000 0000 0000 0001     | 1                | 1                  |

| • • •                   |                  |                    |

| 0111 1111 1111 1110     | 32766            | 32766              |

| 0111 1111 1111 1111     | 32767            | 32767              |

| 1000 0000 0000 0000     | 32768            | <del>-</del> 32768 |

| 1000 0000 0000 0001     | 32769            | -32767             |

|                         |                  |                    |

| 1111 1111 1111 1110     | 65534            | -2                 |

| 1111 1111 1111 1111     | 65535            | -1                 |

Allowable range:

$$0 \le X \le 2^{16} - 1$$

$$-2^{15} \le X \le 2^{15} - 1$$

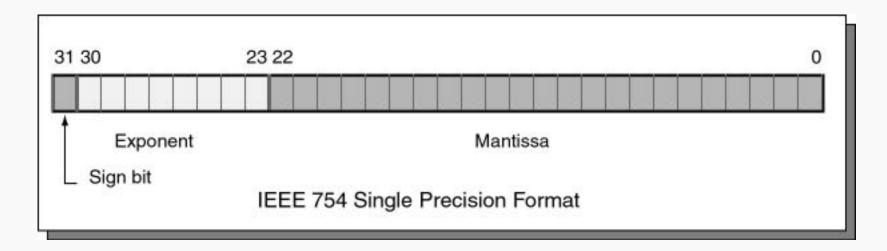

# Floating Point Numbers Representation

#### FP numbers doesn't exist in BComp!

$$X = (-1)^{(sign)} x (1 + Mantissa) x 2^{(exponent-127)}$$

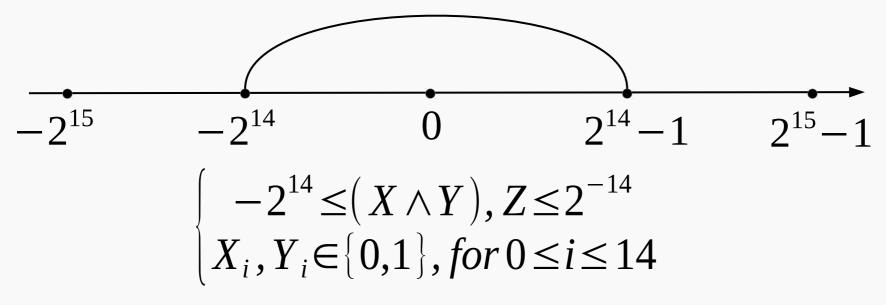

# Logical Values Representation

- 1 = true, 0 = false

- 16-bit number contains 16 logical values

$$X_i \in \{0,1\}$$

for  $0 \le i \le 15$

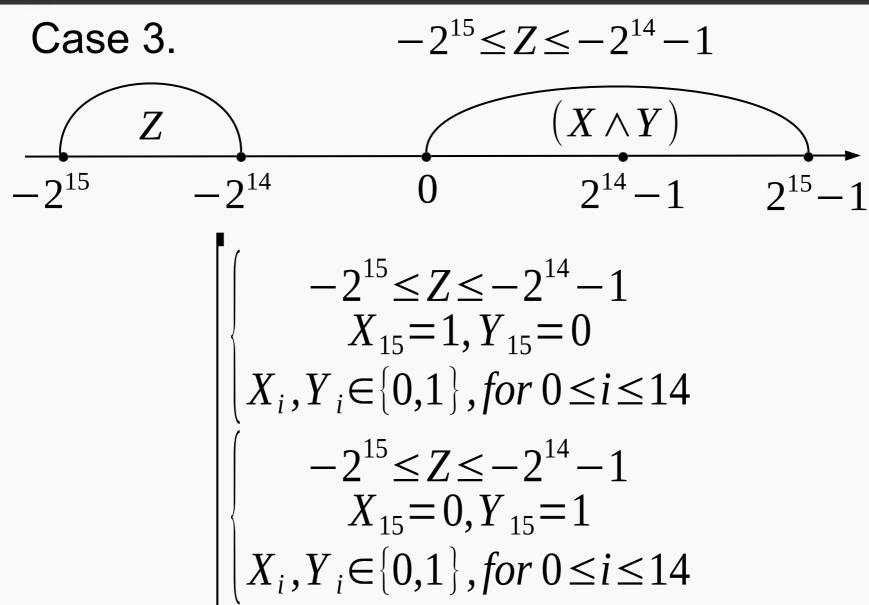

• R=(X&Y)+Z

### Representation Area:

- R is signed 16-bit number

- X, Y are the sets of the 16 one-bit logical values

- Z is signed 16-bit number

- Result of the logical operation X&Y is interpreted as arithmetic operand:

- (X&Y) is signed 16-bit number

Allowable values for R=(X&Y)+Z:

For R:

$$-2^{15} \le R \le 2^{15} - 1$$

Case 1. We can prevent overflow by the limitation of the size of the operands for addition operation:

In cause of these limits we've lost the half of the possible values for the (X&Y) & Z. It's not good!

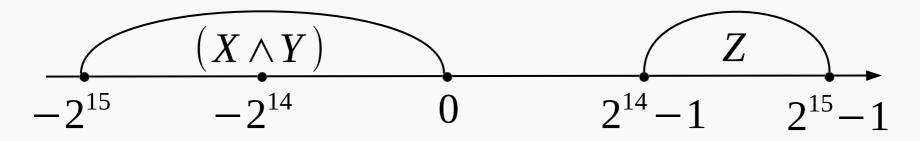

Case 2.

$$2^{14} \le Z \le 2^{15} - 1$$

$$\begin{cases} 2^{14} \le Z \le 2^{15} - 1 \\ X_{15} = 1, Y_{15} = 1 \\ X_i, Y_i \in \{0, 1\}, for \ 0 \le i \le 14 \end{cases}$$

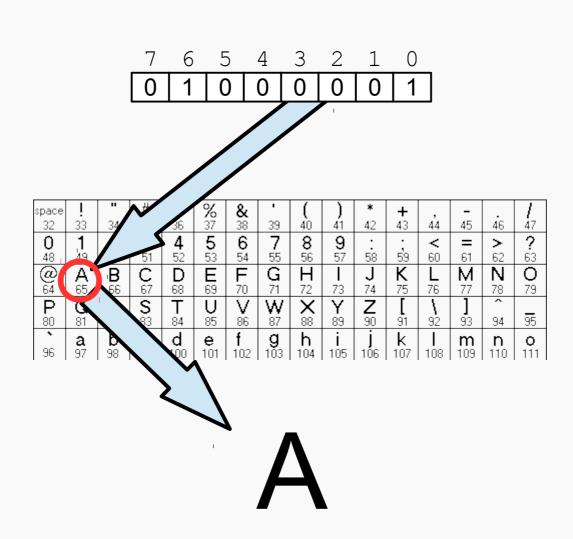

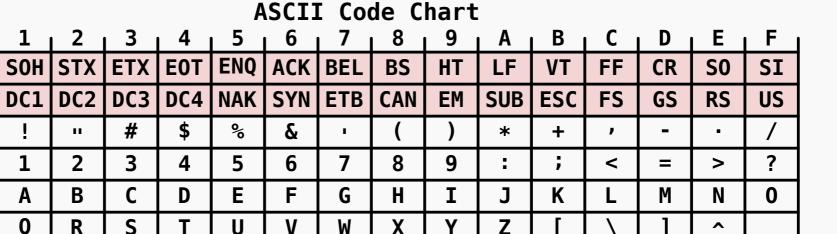

# Text Data Representation

NUL

DLE

@

p

a

q

b

C

d

t

e

u

V

## **ASCII Symbols**

i

k

Z

m

n

0

**DEL**

h

X

7 bits for each symbol! The 8th bit is used for parity check.

g

### UNICODE, UTF-8

#### Code point

#### UTF-8 encoded

| plane                        | row                          | column                       |          | byte 0                                            | byte 1          | byte 2                       | byte 3         |

|------------------------------|------------------------------|------------------------------|----------|---------------------------------------------------|-----------------|------------------------------|----------------|

|                              |                              |                              |          |                                                   |                 |                              |                |

| 00000000                     | 0 0 0 0,0 0 0 0              | 0 x x x x x x x              | 7x       | $0 \times \times \times_{I} \times \times \times$ |                 |                              |                |

| 0 0 0 0 0 0 0 0              | 0 0 0 0 0 × × ×              | x x y y <sub>1</sub> y y y y | 5x6y     | 1 1 0 × × × × ×                                   | 1 0 y y y y y y |                              |                |

| 0 0 0 0 0 0 0 0              | x x x x <sub>1</sub> y y y y | y y z z z z z                | 4x6y6z   | 1 1 1 0 x x x x                                   | 1 0 y y y y y y | 1 0 z z z z z z              |                |

| 0 0 0 w <sub>1</sub> w w x x | x x x x <sub>1</sub> y y y y | y y z z <sub>ı</sub> z z z z | 3w6x6y6z | 1 1 1 1 <sub>1</sub> 0 w w w                      | 1 0 x x x x x x | 1 0 y y <sub>1</sub> y y y y | 10 z z z z z z |

Cyrillic «A» → unicode \u0410 → 0000 0100 0001 0000

$\rightarrow$  UTF-8 110 1 0000 1001 0000  $\rightarrow$  D0 90

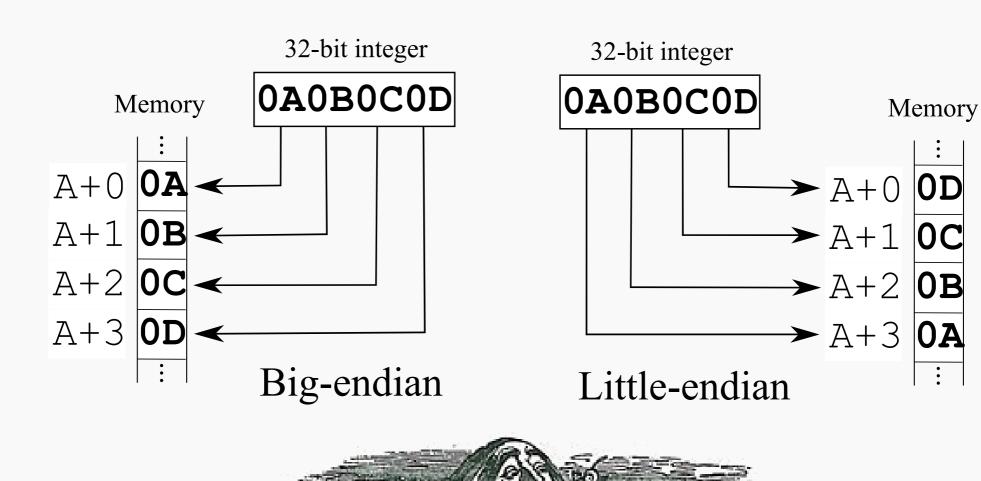

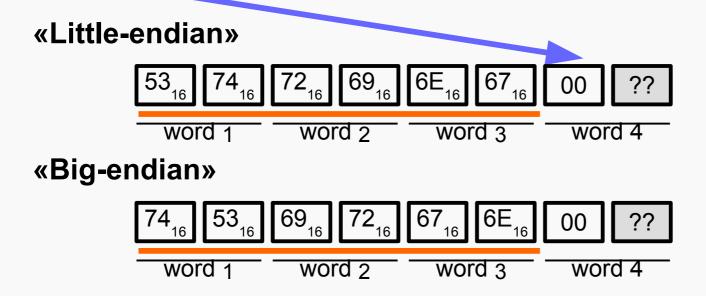

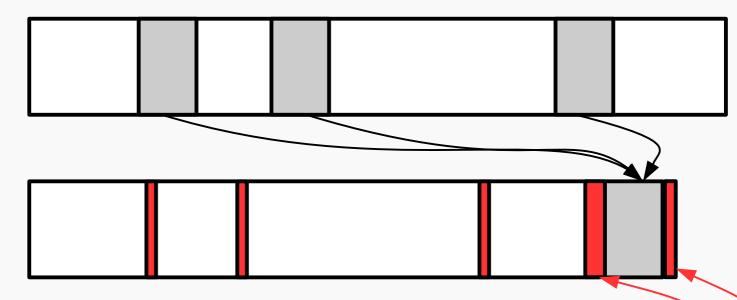

## Big-endian & Little-endian

# String Data Representation

### 1) NUL terminated String

### 2) Packaging with length

# It's all about the hat!

# Performing Equations

5

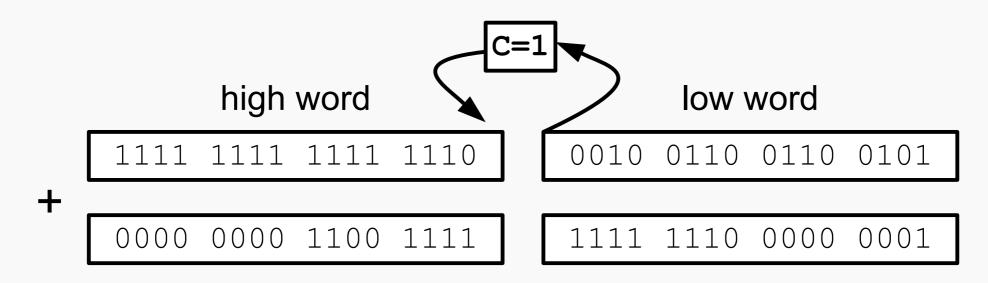

### 32-bit Numbers in BComp

0000 0000 1100 1110

0010 0100 0110 0110

fffe2665 + cffe01 = ce2466 -121243 + 13630977 = 13509734

### Addition of the 32-bit Numbers

| Содержимое |      | ержимое       |                                                            |

|------------|------|---------------|------------------------------------------------------------|

| Address    | Code | Mnemonic name | Comments                                                   |

| 010        | F200 | CLA           |                                                            |

| 011        | 4019 | ADD 19        | Low word of the first number                               |

| 012        | 401B | ADD 1B        | Low word of the second number                              |

| 013        | 301D | MOV 1D        | Saving the low word of the result                          |

| 014        | F200 | CLA           |                                                            |

| 015        | 501A | ADC 1A        | High word of the first number with carry between the words |

| 016        | 401C | ADD 1C        | High word of the second number                             |

| 017        | 301E | MOV 1E        | Saving the high word of the results                        |

| 018        | F000 | HLT           | Halt                                                       |

| 019        | 2665 | X             | Two memory cells contains the first number                 |

| 01A        | FFFE | X             |                                                            |

| 01B        | FE01 | Y             | Two memory cells contains the second number                |

| 01C        | 00CF | Y             |                                                            |

| 01D        | 2466 | R             | Two memory cells contains the result                       |

| 01E        | 00CE | R             |                                                            |

fffe2665 + cffe01 = ce2466

### Change the Sign of the 16-bit Number

|         | Content |               |                                                      |  |

|---------|---------|---------------|------------------------------------------------------|--|

| Address | Code    | Mnemonic name | Comments                                             |  |

| 010     | F200    | CLA           |                                                      |  |

| 011     | 4016    | ADD 16        | X in accumulator register                            |  |

| 012     | F400    | CMA           | Calculate the complement (invert bits of the number) |  |

| 013     | F800    | INC           | Increment                                            |  |

| 014     | 3017    | MOV 17        | Save the result                                      |  |

| 015     | F000    | HLT           |                                                      |  |

| 016     | 0002    | X             | X                                                    |  |

| 017     | FFFE    | R             | R                                                    |  |

$$R = -X$$

### Change the Sign of the 32-bit Number

|         | Content |               |                                                       |  |

|---------|---------|---------------|-------------------------------------------------------|--|

| Address | Code    | Mnemonic name | Comments                                              |  |

| 010     | F200    | CLA           |                                                       |  |

| 011     | 401E    | ADD 1E        | High word of the number X in the accumulator register |  |

| 012     | F400    | CMA           | Calculate the complement (invert bits of the number)  |  |

| 013     | 3020    | MOV 20        | Save the high word of the R number                    |  |

| 014     | F200    | CLA           |                                                       |  |

| 015     | 401D    | ADD 1D        | Low word of the number X in the accumulator register  |  |

| 016     | F400    | CMA           | Calculate the complement (invert bits of the number)  |  |

| 017     | F800    | INC           | Increment (calculate the complement for the low word) |  |

| 018     | 301F    | MOV 1F        | Save the low word                                     |  |

| 019     | F200    | CLA           |                                                       |  |

| 01A     | 5020    | ADC 20        | Add the possible carry bit to the high word           |  |

| 01B     | 3020    | MOV 20        | Save the high word                                    |  |

| 01C     | F000    | HLT           |                                                       |  |

| 01D     | 2665    | X             | $\mathbf{R} = -\mathbf{X}$                            |  |

| 01E     | FFFE    | X             |                                                       |  |

| 01F     | D99B    | R             | R = 121243                                            |  |

| 020     | 0001    | R             |                                                       |  |

#### Computational Process Control

| Branch if carry is set | BCS M | 8XXX | If (C) = 1, then M → IP                |

|------------------------|-------|------|----------------------------------------|

| Branch if plus         | BPL M | 9XXX | If $(N)=0$ , then $M \rightarrow IP$   |

| Branch if minus        | BMI M | AXXX | If (N) = 1, then M → IP                |

| Branch if zero         | BEQ M | BXXX | If $(Z) = 1$ , then $M \rightarrow IP$ |

| Unconditional branch   | BR M  | CXXX | M → IP                                 |

### Calculating the Absolute Value of Number

|         | Content |               |                                                      |  |

|---------|---------|---------------|------------------------------------------------------|--|

| Address | Code    | Mnemonic name | Comments                                             |  |

| 010     | F200    | CLA           |                                                      |  |

| 011     | 4017    | ADD 17        | X value is in accumulator register                   |  |

| 012     | 9015    | BPL 15        | If X>=0 branch to address 15                         |  |

| 013     | F400    | CMA           | Calculate the complement (invert bits of the number) |  |

| 014     | F800    | INC           | Increment                                            |  |

| 015     | 3018    | MOV 18        | Save the result                                      |  |

| 016     | F000    | HLT           |                                                      |  |

| 017     | FFFE    | X             | X                                                    |  |

| 018     | 0002    | R             | R =  X                                               |  |

$$R = |X|$$

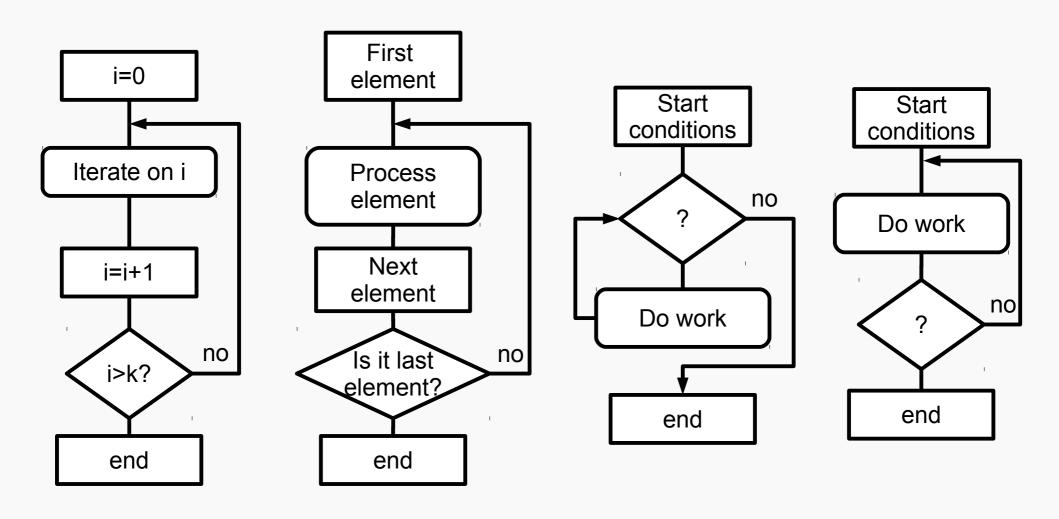

### Digression: Cyclic Programms

• for, foreach, while, do-while

#### R=50Y (case 1)

#### Remember about allowable ranges!

|         | Content |               |                                                                 |

|---------|---------|---------------|-----------------------------------------------------------------|

| Address | Code    | Mnemonic name | Comments                                                        |

| 005     | 0042    | Y             | First operand                                                   |

| 006     | 0000    | Z             | Memory cell for intermediate & final results                    |

| 007     | 0032    | M             | Second operand 50=(32) <sub>16</sub>                            |

| 008     | 0000    | С             | Cycle counter                                                   |

| 010     | F200    | CLA           | Add first operand value Y to intermediate result in memory cell |

| 011     | 4006    | ADD 6         | 6 yet another time                                              |

| 012     | 4005    | ADD 5         |                                                                 |

| 013     | 3006    | MOV 6         |                                                                 |

| 014     | F200    | CLA           | Increment cycle counter C value and save it copy to             |

| 015     | 4008    | ADD 8         | accumulator register                                            |

| 016     | F800    | INC           |                                                                 |

| 017     | 3008    | MOV 8         |                                                                 |

| 18      | 6007    | SUB 7         | If C < M then continue add Y to R                               |

| 19      | A010    | BMI 10        |                                                                 |

| 1A      | F000    | HLT           | Halt when all 50 cycles are completed                           |

#### R=50Y (ISZ)

| Increment and | ISZ M | 0XXX | $M + 1 \rightarrow M$ , if $(M) >= 0$ , then |

|---------------|-------|------|----------------------------------------------|

| skip          |       |      | (IP) + 1 → IP                                |

### Works without usage of the accumulator (A) & carry (C) registers!

|         |      | Content       |                                                           |  |

|---------|------|---------------|-----------------------------------------------------------|--|

| Address | Code | Mnemonic name | Comments                                                  |  |

| 005     | 0042 | Y             | First operand                                             |  |

| 006     | 0000 | R             | Memory cell for intermediate & final results              |  |

| 007     | FFCE | M             | Negative value of the second operand (-50)                |  |

| 010     | F200 | CLA           |                                                           |  |

| 011     | 4005 | ADD 5         | Add first operand Y value to accumulator register content |  |

| 012     | 0007 | ISZ 7         | Increment M. If M<0 perform branch to address 11. If M=0  |  |

| 013     | C011 | BR 11         | skip BR.                                                  |  |

| 014     | 3006 | MOV 6         | Increment cycle counter C value and save it copy to       |  |

| 015     | F000 | HLT           | accumulator register                                      |  |

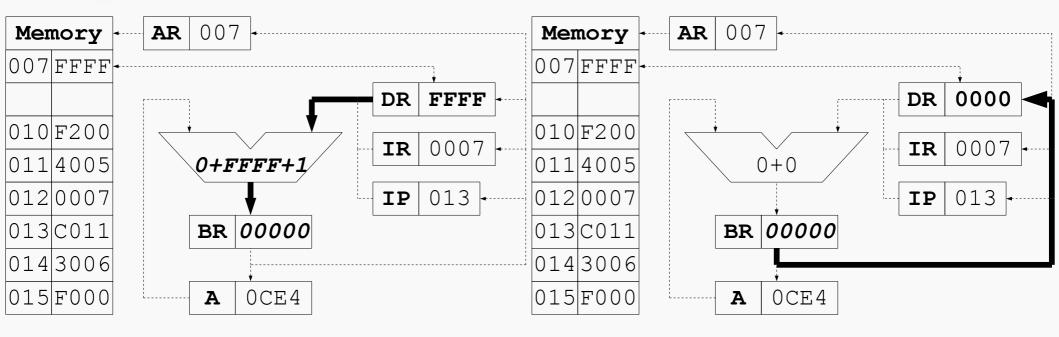

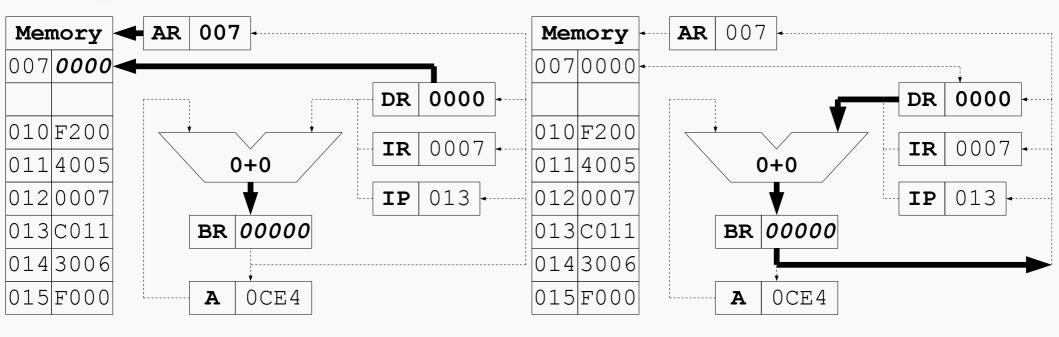

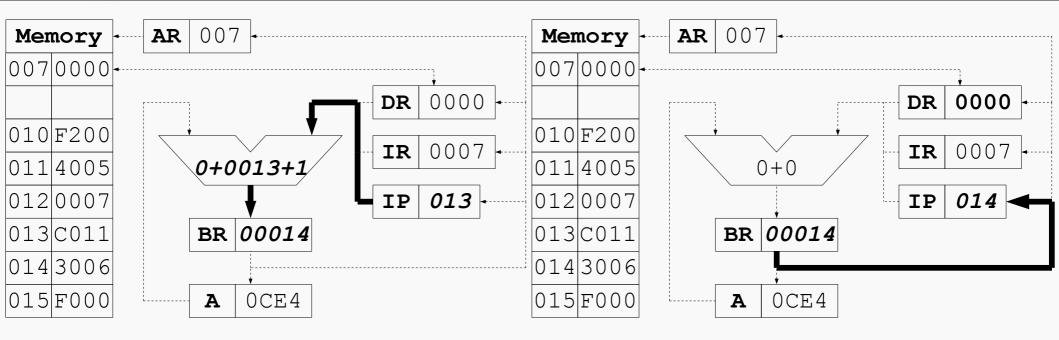

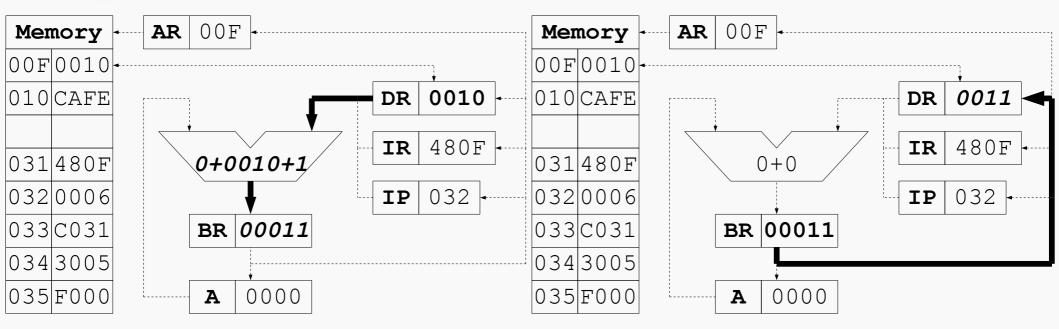

### Execution Cycle of the ISZ Instruction

- 42<sub>16</sub>=66<sub>10</sub>; 50\*66=3300<sub>10</sub>=CE4<sub>16</sub>

- Before cycle DR contains the data from the memory cell (FFFF) from the address part (007) of the ISZ instruction.

- Increment DR content and save it back to DR through BR.

### Execution Cycle of the ISZ Instruction

- Save data from DR to the memory, reset BR.

- Transfer the 15th bit of the DR content to compare scheme where it checks for equality with 1.

### Execution Cycle of the ISZ Instruction

Increment IP content because the 15th bit of the DR content equals 0.

### R=50Y («chinese code», optimal)

|         |      | Content  |                                                     |  |

|---------|------|----------|-----------------------------------------------------|--|

| Address | Code | Mnemonic | Comments                                            |  |

|         |      | name     |                                                     |  |

| 005     | 0078 | Y        | First operand                                       |  |

| 006     | 0000 | R        | Memory cell for intermediate & final results        |  |

| 007     | 0000 | R'       | Intermediate result Y*16                            |  |

| 010     | F200 | CLA      |                                                     |  |

| 011     | 4005 | ADD 5    | Y                                                   |  |

| 012     | F600 | ROL      | Y*2 after ADD C=0. No need for CLC instruction call |  |

| 013     | 3006 | MOV 6    | Save R to the memory cell                           |  |

| 014     | F300 | CLC      |                                                     |  |

| 015     | F600 | ROL      | $^{9^{+4}}$ $50_{10} = 32_{16} = 00110010_{2}$      |  |

| 016     | F300 | CLC      |                                                     |  |

| 017     | F600 | ROL      | Y*8                                                 |  |

| 018     | F300 | CLC      |                                                     |  |

| 019     | F600 | ROL      | Y*16                                                |  |

| 01A     | 3007 | MOV 7    | Save R' to the memory cell                          |  |

| 01B     | F300 | CLC      |                                                     |  |

| 01C     | F600 | ROL      | Y*32                                                |  |

| 01D     | 4007 | ADD 7    | Add R & R' to the accumulator register content      |  |

| 01E     | 4006 | ADD 6    | R=32Y+16Y+2Y=(32+16+2)Y                             |  |

| 01F     | 3006 | MOV 6    | Save the result                                     |  |

| 020     | F000 | HLT      |                                                     |  |

# One-Dimensional Arrays Representation

|       | •             |                | •           |             | -          |

|-------|---------------|----------------|-------------|-------------|------------|

| 1. Ea | ch elemeni    | t of the arra  | y has a l   | ength:o     | f one word |

|       | Element 0     | Element 1      |             | Ξ           | Element n  |

|       | word 0        | word 1         |             | :           | word n     |

| 2. If | element len   | gth is less    | than wor    | d :         |            |

|       | Element 0     | Element 1      |             |             | Element n  |

|       | word 0        | word 1         |             | :           | word n     |

|       | Element 0 Ele | ment 1 Element | 2           | nt n-1      | Element n  |

|       | word 0        | word 1         | :           | :           | word k     |

| 3. If | element len   | gth is grea    | ter than v  | vord        |            |

|       | Element (     | Ele            | ment 1      | Eler        | ment n     |

|       | word 0        | word 1         |             | · · · · · · | word p     |

|       | Elem          | ent 0          | } $\square$ | Elemei      | nt n       |

|       | word 0        | word 1         | • Wor       |             | word n     |

# Sum of the Array Elements (Readressing)

|                                               |                                                      | Content               |                                                                                                                                                                       |  |

|-----------------------------------------------|------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Address                                       | Code                                                 | Mnemonic name         | Comments                                                                                                                                                              |  |

| 005<br>006                                    | 0000<br>FFE0                                         | S<br>C                | Memory cell for intermediate & final results Negative value of the array size (-32)                                                                                   |  |

| 010<br><br>02F                                |                                                      |                       | Array elements                                                                                                                                                        |  |

| 030<br>031<br>032<br>033                      | F200<br>4005<br>4010<br>3005                         | CLA ADD 5 ADD ? MOV 5 | Add result of the previous iteration (S) to the content of the memory cell set in the code of the instruction with address 32 and save it to S                        |  |

| 034<br>035<br>036<br>037<br>038<br>039<br>03A | F200<br>4032<br>F800<br>3032<br>0006<br>C030<br>F000 |                       | Get the code of the instruction with address 32 Increment it Save it into memory cell 32 Was it last element of the array? If no – branch to address 30 If yes – halt |  |

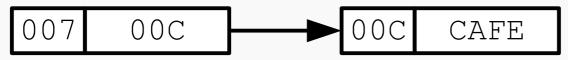

#### Indirect Addressing & Index Cells

1. Direct addressing

| 010 | CLA |   |

|-----|-----|---|

| 011 | ADD | 7 |

2. Indirect addressing

| 010 | CLA |     |

|-----|-----|-----|

| 011 | ADD | (7) |

3. Indirect autoincrement addressing (memory cells 8-F)

| 010 | CLA |     |

|-----|-----|-----|

| 011 | ADD | (F) |

# Sum of the Array Elements (Indirect Addressing)

|         | Content |               |                                                             |  |

|---------|---------|---------------|-------------------------------------------------------------|--|

| Address | Code    | Mnemonic name | Comments                                                    |  |

| 005     | 0000    | S             | Memory cell for intermediate & final results                |  |

| 006     | FFE0    | С             | Negative value of the array size (-32)                      |  |

| 007     | 0010    | I             | Current element of the array                                |  |

| 010     |         |               |                                                             |  |

|         |         |               | Array elements                                              |  |

| 02F     |         |               |                                                             |  |

| 030     | F200    | CLA           |                                                             |  |

| 031     | 4807    | ADD (7)       | Accumulator register contains the next element of the array |  |

| 032     | 0007    | ISZ 7         | Increment element's address without A content change        |  |

| 033     | F100    | NOP           | This instruction never will be executed                     |  |

| 034     | 0006    | ISZ 6         | Was it the last element of the array?                       |  |

| 035     | C031    | BR 31         | If no – continue calculating                                |  |

| 036     | 3005    | MOV 5         | Result is in memory cell 5                                  |  |

| 037     | F000    | HLT           |                                                             |  |

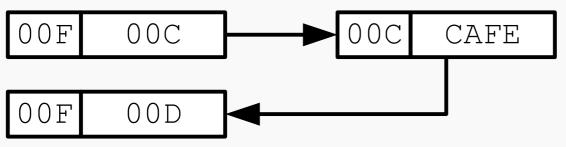

# Sum of the Array Elements (Indirect Autoincrement Addressing)

|         | Content |               |                                                                                                        |  |

|---------|---------|---------------|--------------------------------------------------------------------------------------------------------|--|

| Address | Code    | Mnemonic name | Comments                                                                                               |  |

| 005     | 0000    | S             | Memory cell for intermediate & final results                                                           |  |

| 006     | FFE0    | С             | Negative value of the array size (-32)                                                                 |  |

|         |         |               |                                                                                                        |  |

| 00F     | 0010    | I             | Current element of the array                                                                           |  |

| 010     |         |               |                                                                                                        |  |

|         |         |               | Array elements                                                                                         |  |

| 02F     |         |               |                                                                                                        |  |

| 030     | F200    | CLA           |                                                                                                        |  |

| 031     | 480F    | ADD (F)       | Accumulator register contains the next element of the array Increment the content of the F memory cell |  |

| 032     | 0006    | ISZ 6         | Was it the last element of the array?                                                                  |  |

| 033     | C031    | BR 31         | If no – continue calculating                                                                           |  |

| 034     | 3005    | MOV 5         | Result is in memory cell 5                                                                             |  |

| 035     | F000    | HLT           |                                                                                                        |  |

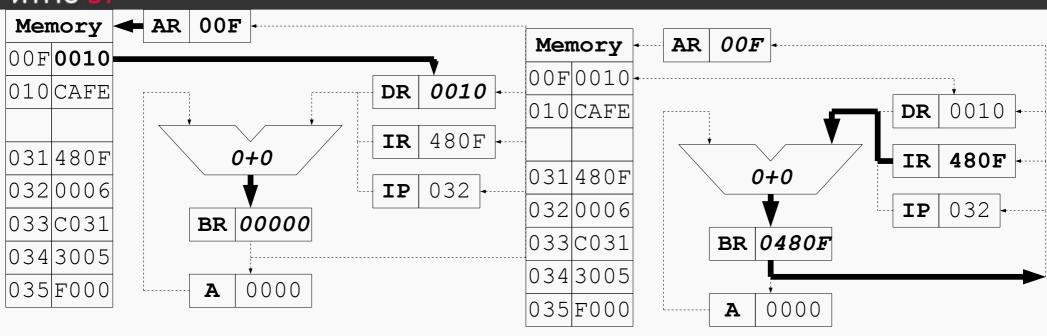

- In the end of the instruction fetch cycle IP was incremented and code 480F of the current instruction ADD (F) was saved into DR & IP

- On the next step lower 11 bits of the DR content transfers into AR through BR

### итмо вт

- Save the content of the AR to DR

- Sequentially check lower bits of the IR content for compliance with mask 000 0000 1XXX, i.e. check is it index cell (008-00F) or not

- If it is index cell increment it content in DR and save it to BR

- Transfer incremented content of BR to DR

- Save the new, incremented content of the index cell into the memory

- On the next step we will need to use the old value (on the operand fetch cycle) so the content of the DR decrements, saves to BR and on the next clock saves back to DR (DR+COM(0)=DR-1 → BR→ DR)

### Подпрограммы

6

#### Мотвивация

• Зачем?

- Когда выгодно создавать подпрограмму?

- Размер кода

- Передача и обработка параметров;

возвращение результатов

- Инлайнинг обратный процесс

### БЭВМ: Вызов программы и возврат из нее

Основная программа

Подпрограмма

### Передача параметров и получение результатов

- Аккумулятор (Регистры Общего Назначения)

- Сколько параметров можно передать в БЭВМ?

- Адресуемые ячейки памяти

- Необходимо организовать

- Стек

- Регистровые окна

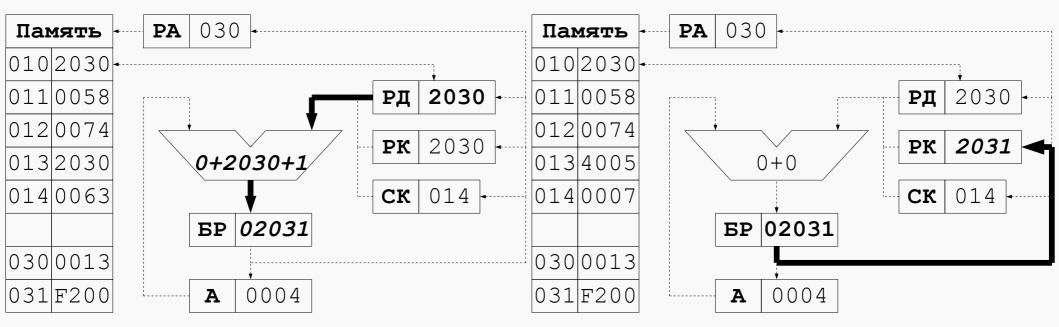

### Комплекс программ: передача параметров через аккумулятор

Подпрограмма вычисления удвоенного модуля для чисел в ячейках 58,63,71 с размещением результатов в ячейках 74,77,82

| <b>A</b> = p.o.o. | Содержимое |           | Коммонтории    |

|-------------------|------------|-----------|----------------|

| Адрес             | Код        | Мнемоника | Комментарии    |

| 010               | F200       | CLA       | Первое число   |

| 011               | 4058       | ADD 58    | Аргумент в 58  |

| 012               | 2030       | JSR 30    |                |

| 013               | 3074       | MOV 74    | Результат в 74 |

| 014               | F200       | CLA       | Первое число   |

| 015               | 4063       | ADD 63    | Аргумент в 63  |

| 016               | 2030       | JSR 30    |                |

| 017               | 3077       | MOV 77    | Результат в 77 |

| 18                | F200       | CLA       | Первое число   |

| 19                | 4071       | ADD 71    | Аргумент в 71  |

| 1A                | 2030       | JSR 30    |                |

| 1B                | 3082       | MOV 82    | Результат в 82 |

| 1C                | F000       | HLT       |                |

Подпрограмма вычисления R=2|X|

| <b>Л</b> прос | Содержимое |             |  |

|---------------|------------|-------------|--|

| Адрес         | Код        | Мнемоника   |  |

| 030           | 0000       | Адрес возв. |  |

| 031           | 9034       | BPL 34      |  |

| 032           | F400       | CMA         |  |

| 033           | F800       | INC         |  |

| 034           | F300       | CLC         |  |

| 035           | F600       | ROL         |  |

| 036           | C830       | BR (30)     |  |

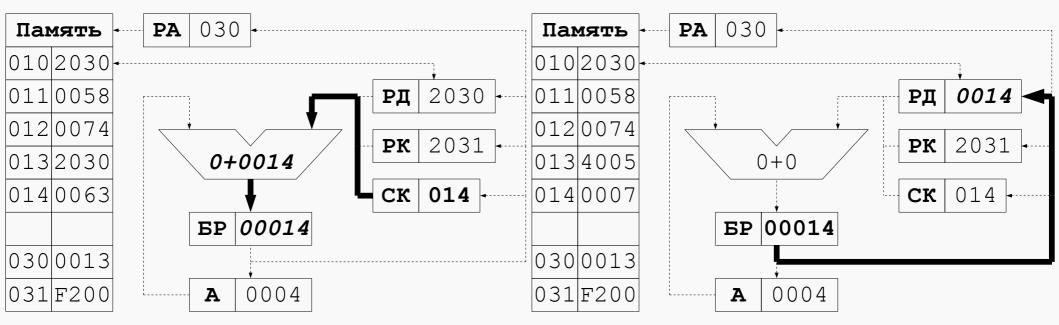

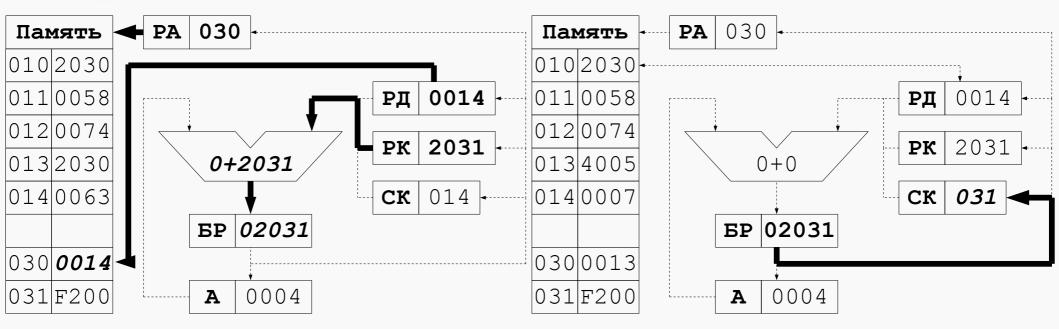

### Комплекс программ: передача через адреса ячеек памяти

Подпрограмма вычисления R=2|X|

#### Основная программа

| <b>Л</b> прос | Содержимое |           |  |

|---------------|------------|-----------|--|

| Адрес         | Код        | Мнемоника |  |

| 010           | 2030       | JSR 30    |  |

| 011           | 0058       | Адрес Х1  |  |

| 012           | 0074       | Адрес R1  |  |

| 013           | 2030       | JSR 30    |  |

| 014           | 0063       | Адрес Х2  |  |

| 015           | 0077       | Адрес R2  |  |

| 016           | 2030       | JSR 30    |  |

| 017           | 0071       | Адрес ХЗ  |  |

| 018           | 0082       | Адрес R3  |  |

| 019           | F000       | HLT       |  |

| <b>Л</b> прос | Содержимое |             | <b>Коммонтории</b> |

|---------------|------------|-------------|--------------------|

| Адрес         | Код        | Мнемоника   | Комментарии        |

| 030           | 0000       | Адрес возв. |                    |

| 031           | F200       | CLA         | По адресу возврата |

| 032           | 4830       | ADD (30)    | выбрать адрес Хі и |

| 033           | 3035       | MOV 35      | записать в яч. 035 |

| 034           | 0030       | ISZ 30      | Адрес возврата++   |

| 035           | 0000       | Адрес Хі    | СК>0 всегда!       |

| 036           | F200       | CLA         | По адресу возврата |

| 037           | 4830       | ADD (30)    | выбрать адрес Ri и |

| 038           | 303A       | MOV 3A      | записать в яч. 03А |

| 039           | 0030       | ISZ 30      | Адрес возврата++   |

| 03A           | 0000       | Адрес Ri    | СК>0 всегда!       |

| 03B           | F200       | CLA         |                    |

| 03C           | 4835       | ADD (35)    | Выбрать Хі         |

| 03D           | 9040       | BPL 40      |                    |

| 03E           | F400       | CMA         | Xi<0, меняем знак  |

| 03F           | F800       | INC         |                    |

| 040           | F300       | CLC         | Умножаем на 2      |

| 041           | F600       | ROL         |                    |

| 042           | 383A       | MOV (3A)    | Записываем Ri      |

| 043           | C830       | BR (30)     | Возврат            |

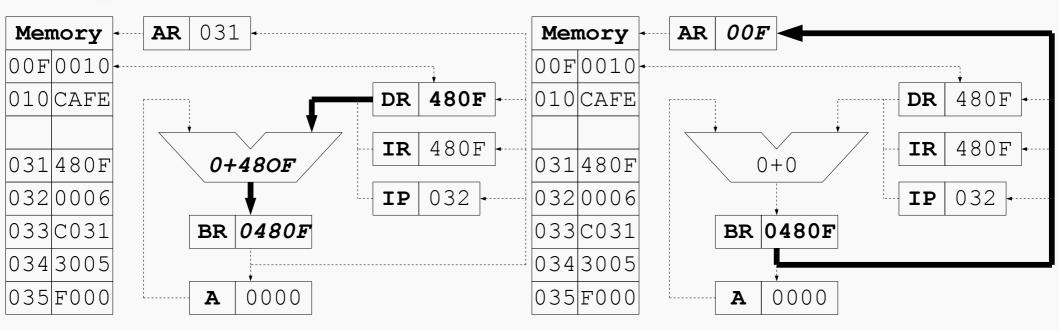

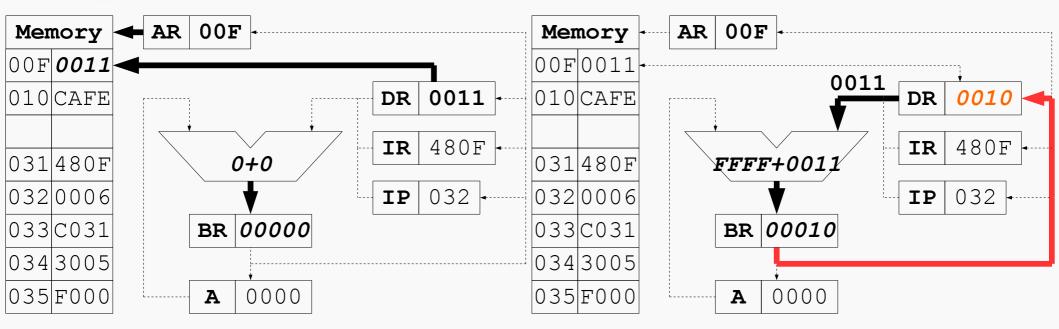

#### Цикл исполнения JSR

- Окончание декодирования адресной команды записывает в РА адресную часть команды

- Содержимое РД увеличивается на 1 и через БР помещается на временное хранение в РК, который не будет больше использоваться в декодировании

#### Цикл исполнения JSR

• Адрес возврата из подпрограммы (014 — содержимое СК) записывается через БР в РД

#### Цикл исполнения JSR

- Содержимое адреса возврата записывается в первую ячейку подпрограммы, одновременно РК переписывается в БР

- Младшие 11 бит содержимого БР записывается в СК, происходит переход к первой команде подпрограммы

#### Цикл исполнения BR (адр)

Чем отличается от цикла исполнения BR адр из лекции 5?

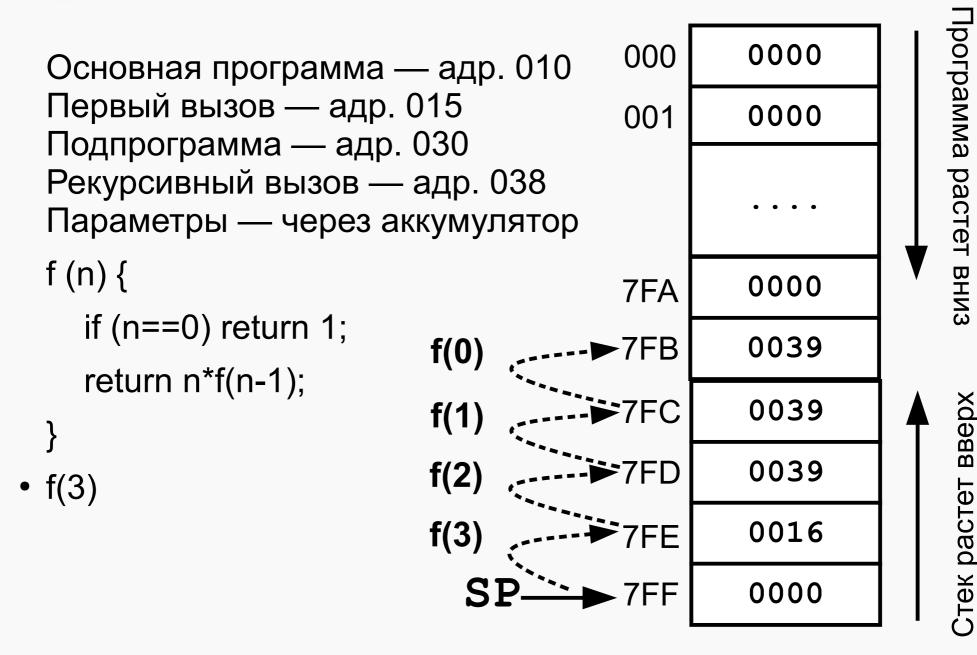

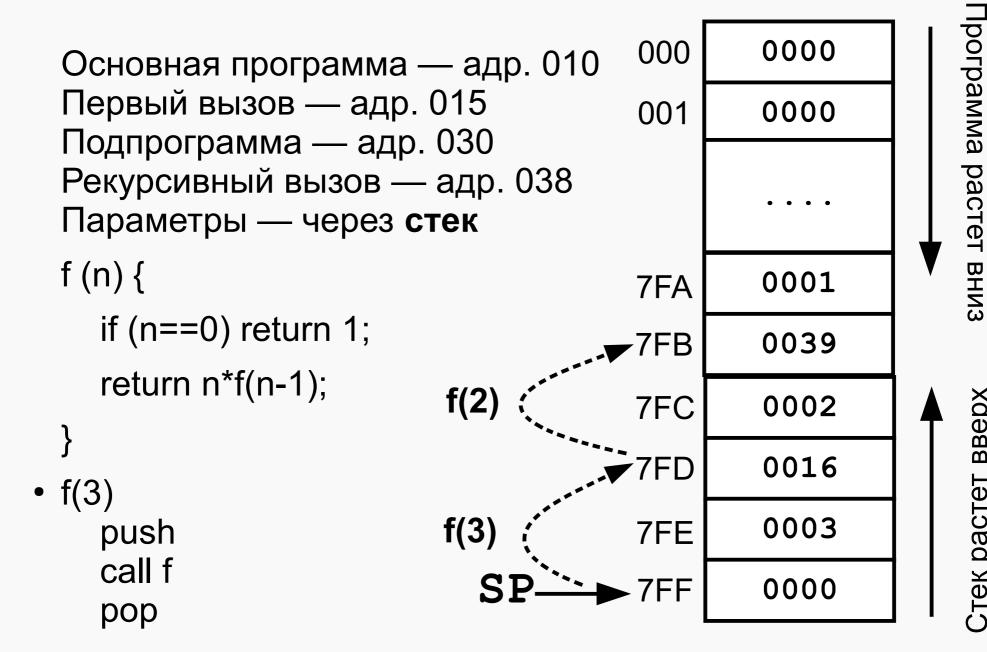

#### Рекурсивность

- Рекурсивность способность подпрограммы вызывать саму себя.

- Подсчет факториала

```

f (n) {

if (n==0) return 1;

return n*f(n-1);

}

```

• В БЭВМ?

| <b>Л</b> прос | Содержимое |             |  |

|---------------|------------|-------------|--|

| Адрес         | Код        | Мнемоника   |  |

| 030           | 0000       | Адрес возв. |  |

| 031           | 9034       | BEQ 37      |  |

| 032           | F500       | DEC         |  |

| 033           | 2030       | JSR 30      |  |

| 034           |            | •••         |  |

| 040           | C830       | BR (30)     |  |

#### Реентерабельность R=50Y

### • Реентерабельность — способность программы быть запущенной несколько раз

| <b>A</b> = p.o.o. | Содержимое |           | Комментарии                                        |  |

|-------------------|------------|-----------|----------------------------------------------------|--|

| Адрес             | Код        | Мнемоника | комментарии                                        |  |

| 005               | 0042       | Y         | Множимое                                           |  |

| 006               | 0000       | R         | Ячейка для накопления и хранения результата        |  |

| 007               | 0000       | M         | Текущее (цикловое) значение множетеля              |  |

| 008               | FFCE       | Мнач      | Начальное отрицательное значение множителя (-50)   |  |

| 00C               | F200       | CLA       |                                                    |  |

| 00D               | 3006       | MOV 6     | Очистка ячейки для накопления результата           |  |

| 00E               | 4008       | ADD 8     | Инициализация текущего множителя                   |  |

| 00F               | 3007       | MOV 7     | начальным значением                                |  |

| 010               | F200       | CLA       | К содержимому аккумулятора добавляется Ү           |  |

| 011               | 4005       | ADD 5     | М наращивается на 1, в случае если М<0             |  |

| 012               | 0007       | ISZ 7     | выполняется переход на 11 адрес. Если M=0, то BR   |  |

| 013               | C011       | BR 11     | пропускается.                                      |  |

| 014               | 3006       | MOV 6     | Содержимое счетчика циклов С увеличивается на 1, а |  |

| 015               | F000       | HLT       | его копия пока сохраняется в аккумулятор           |  |

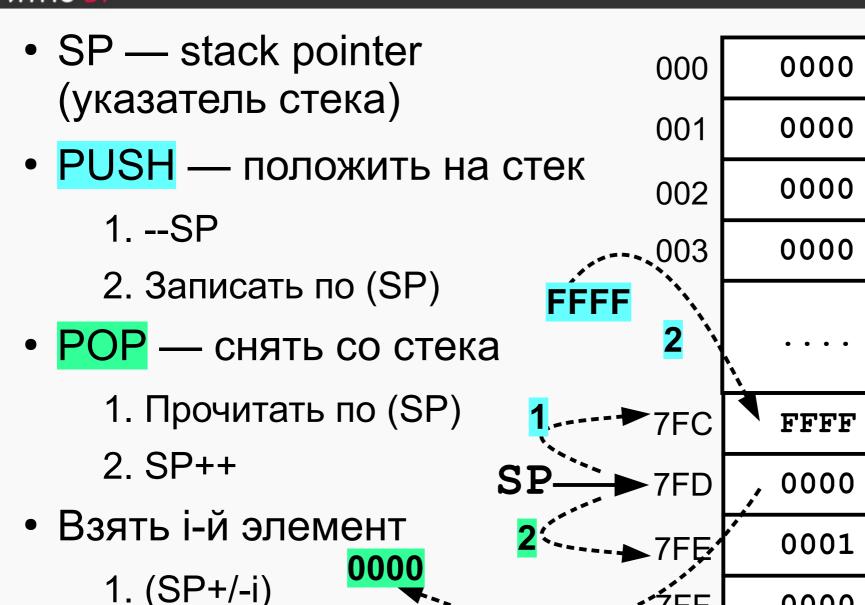

#### Стек

Трограмма

растет вниз

0000

### Вызов подпрограмм с использованием стека

### Передача параметров с использованием стека

### Ассемблер БЭВМ

| Назначение              | Синтаксис                                                  | Пример использования                                          |

|-------------------------|------------------------------------------------------------|---------------------------------------------------------------|

| Размещение в памяти     | ORG адрес                                                  | ORG 10                                                        |

| Прямая<br>адресация     | [метка:] МНЕМОНИКА АРГУМЕНТ                                | MOV R                                                         |

| Косвенная<br>адресация  | [метка:] МНЕМОНИКА (АРГУМЕНТ)                              | ADD (K)                                                       |

| Безадресная<br>команда  | [метка:] МНЕМОНИКА                                         | BEGIN: CLA                                                    |

| Команда<br>ввода-вывода | [метка:] МНЕМОНИКА АДРЕСВУ                                 | OUT 3                                                         |

| Константы               | [метка:] WORD знач. [,знач] [метка:] WORD кол. DUP (знач.) | X: WORD ? Y: WORD X VALUES: WORD 1,2,3 ARRAY: WORD 10 DUP (?) |

### Ассемблер БЭВМ

|        | Подсч | ет отрицательных элементов массива |

|--------|-------|------------------------------------|

| ORG    | 00D   |                                    |

| K:     | WORD  | ? ; Адрес первого элемента массива |

| N:     | WORD  | ? ; Количество элементов массива   |

| R:     | WORD  | ? ; Результат                      |

| BEGIN: | CLA   | ; Первая команда — адрес 010       |

|        | MOV   | R                                  |

|        | ADD   | (K)                                |

|        | BPL   | SKIP                               |

|        | CLA   |                                    |

|        | ADD   | R                                  |

|        | INC   |                                    |

|        | MOV   | R                                  |

| SKIP:  | ISZ   | N                                  |

|        | BR    | BEGIN                              |

|        | HLT   |                                    |

|        |       |                                    |

| ORG    | 020   |                                    |

| X:     | WORD  | 6 DUP (?) ; Элементы массива       |

# PIC - Position Independent Code (перемещаемый код)

• Код, который работает относительно того адреса на который загружен

| <b>Л</b> прос | Содержимое |           |  |  |

|---------------|------------|-----------|--|--|

| Адрес         | Код        | Мнемоника |  |  |

| 010           | F200       | CLA       |  |  |

| 011           | 4017       | ADD 17    |  |  |

| 012           | 9015       | BPL 15    |  |  |

| 013           | F400       | CMA       |  |  |

| 014           | F800       | INC       |  |  |

| 015           | 3018       | MOV 18    |  |  |

| 016           | F000       | HLT       |  |  |

| 017           | FFFE       | X         |  |  |

| 018           | 0002       | R=   X    |  |  |

- Относительная (СК) адресация

- ADD +5 ;(12+5=17)

- BPL +2

- Адресация относительно базового адреса

- ADD 17+0

- MOV 17+1

- Сегментная адресация

- Code-, Data-, StackSegment

- 17 → DS; MOV DS:1

- Выполняется транслятором ассемблера из обычных меток и загрузчиком программы

# Загрузчик и динамический линковщик программ

- Любая ОС имеет соответствующую программу или часть ядра

- Загрузка по выбранному ОС адресу (даже в виртуальной памяти)

- Изменение константных частей адресов в программе

- Загрузка базовых значений регистров

- Динамическая загрузка разделяемых библиотек

- Связывание адресов основной программы с вызываемыми библиотеками

# итмо вт

#### Библиотеки

- Набор стандартных библиотечных функций

- Разделяемые (динамически линкуемые) и архивные (статически линкуемые)

- # find /lib /usr/lib -name "\*.so" |wc -l

3510

- Статические связывают вызовы функций с телом функции в процессе компиляции

- Динамические в момент загрузки

- Если вам нужна функция см. в библиотеки

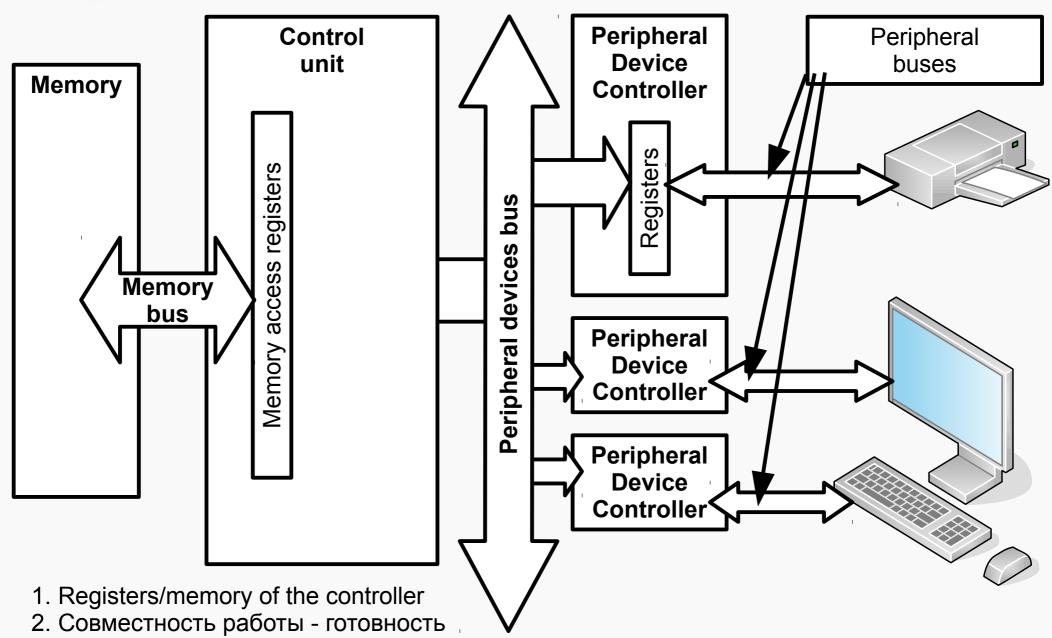

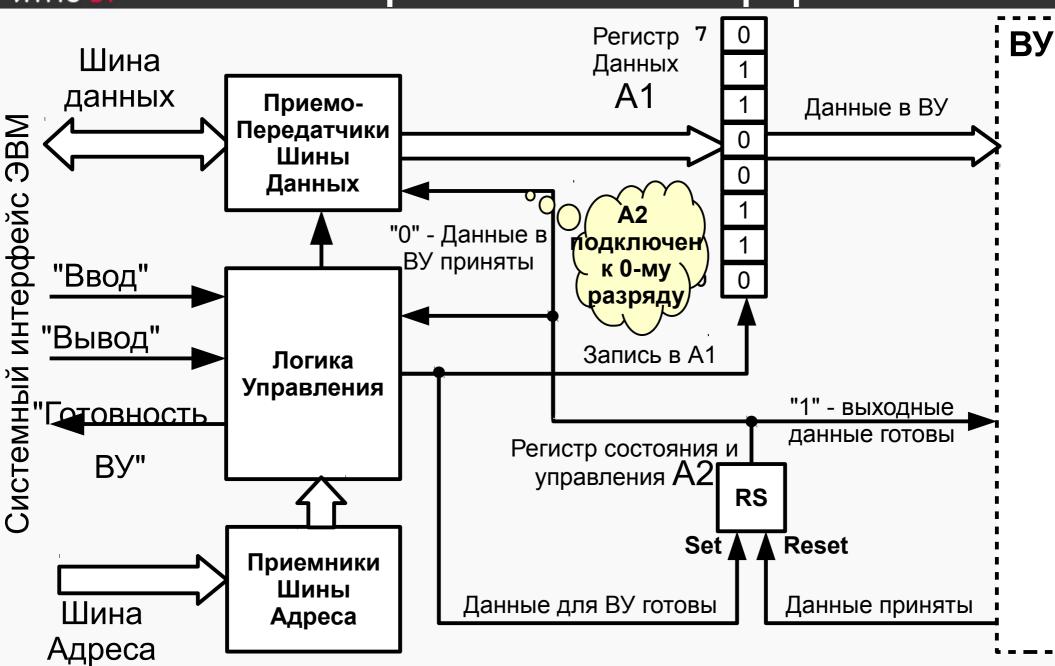

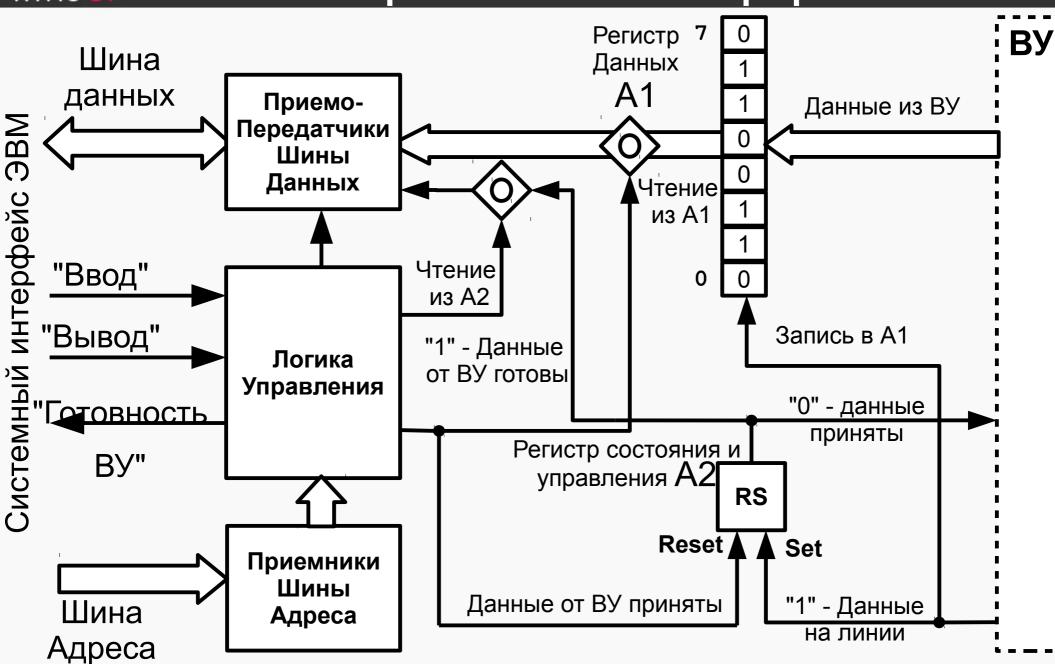

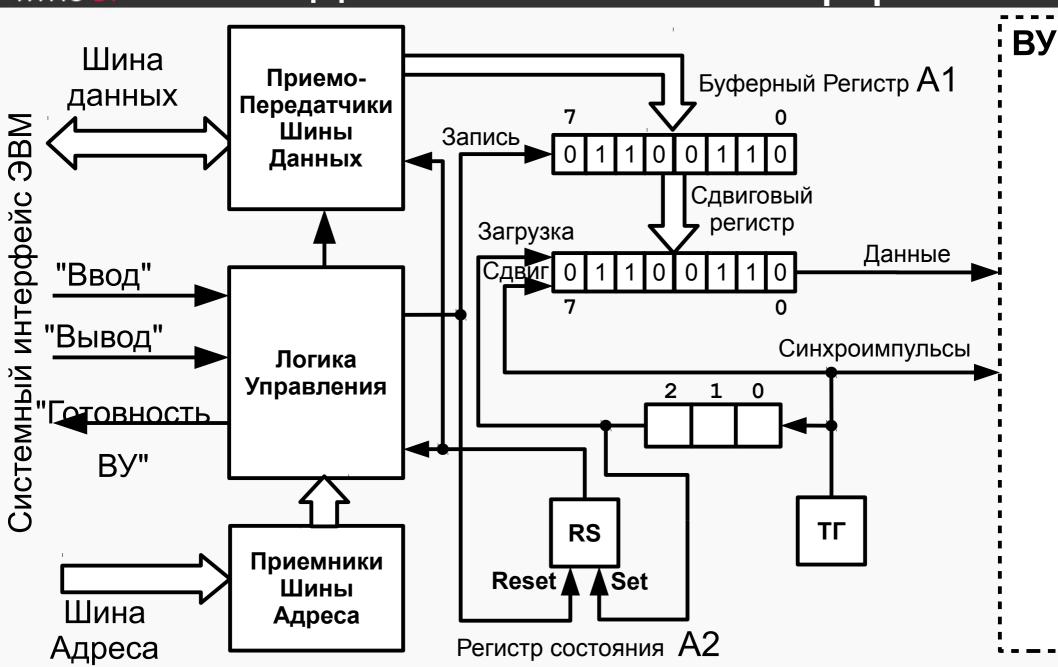

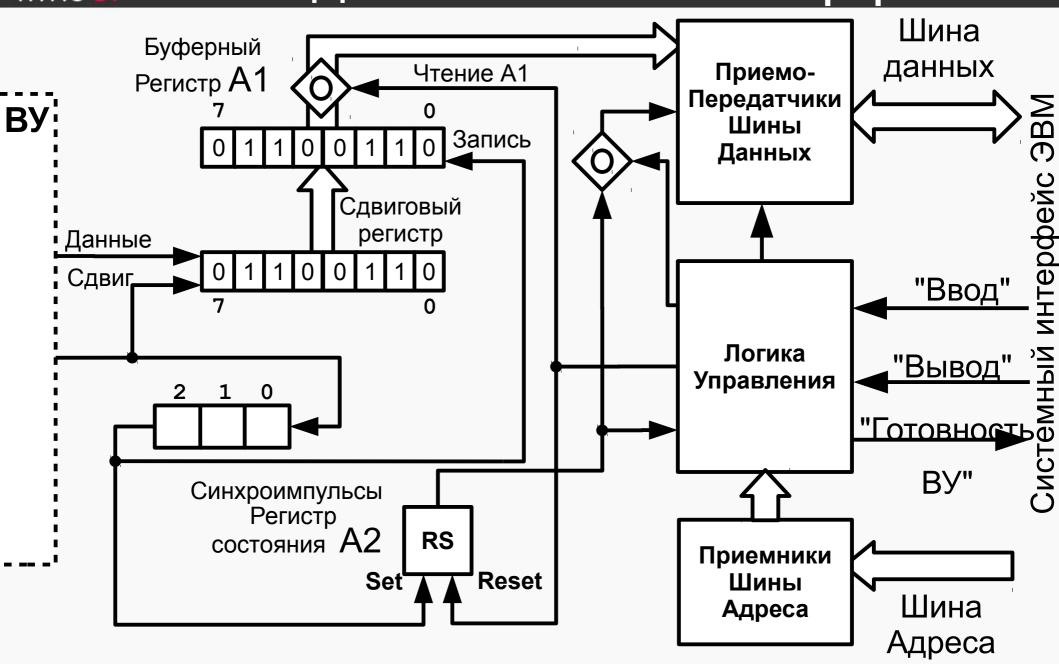

## Input / Output

7

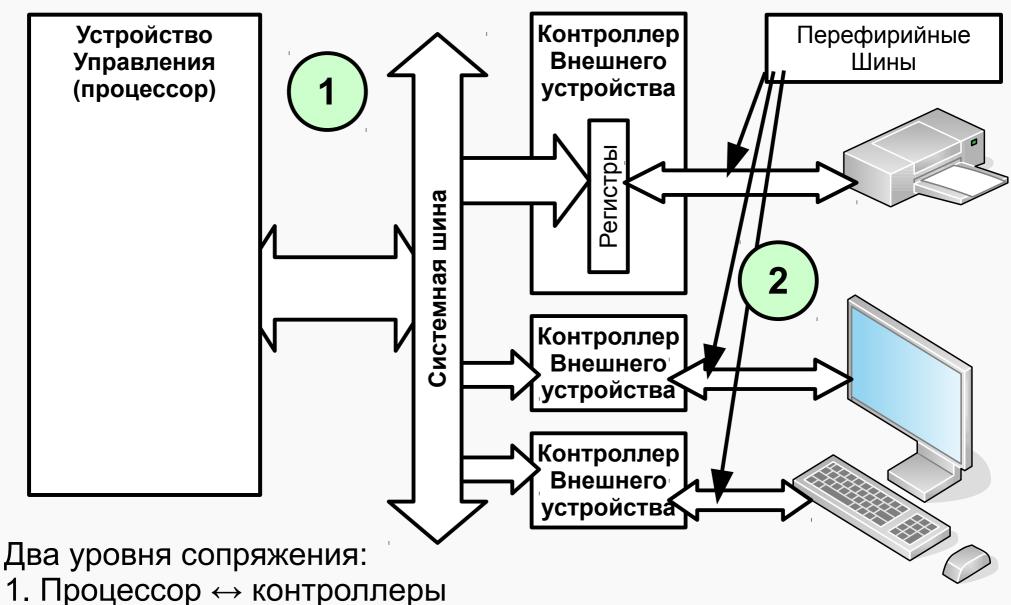

### Connecting Devices to Computer

#### **Drivers**

- Organizes collaboration with devices.

- «Knows» about device work principles, register addresses and supported work modes.

- Are managed by the uniform program interface.

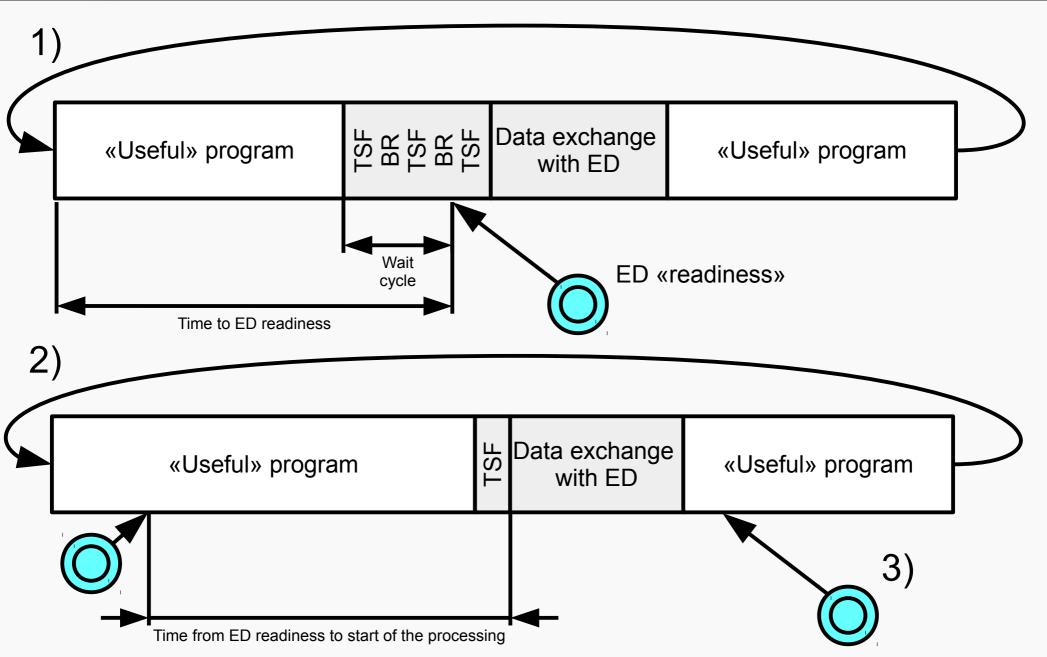

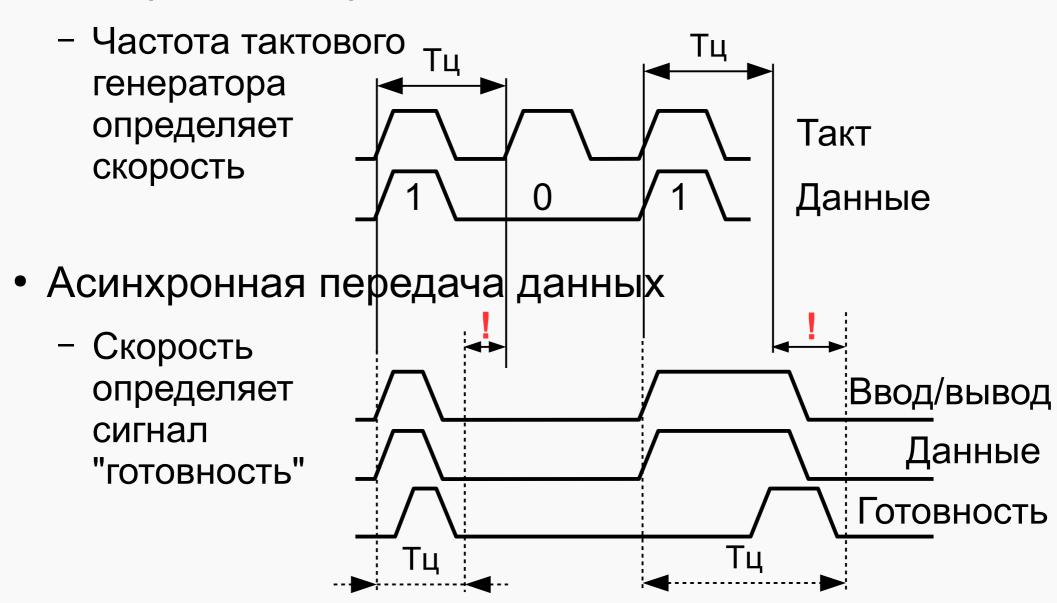

#### Input / Output

Programmed (PIO)

Direct Memory Access (DMA)

- Data exchange initiation:

- Synchronous

- Asynchronous

- Interrupt-driven

- Data transfer:

- Synchronous/Asynchronous

- Data exchange finish and results receiving by driver (or other program):

- Synchronous/Asynchronous

### BComp I/O Instructions

| Name       | Mnemonic name | Code | Description                                |

|------------|---------------|------|--------------------------------------------|

| Clear flag | CLF B         | E0XX | 0 → device flag                            |

| Check flag | TSF B         | E1XX | If (device flag B) = 1, then (IP) + 1 → IP |

| Input      | IN B          | E2XX | (B) → A                                    |

| Output     | OUT B         | E3XX | (A) → B                                    |

#### Команды ввода-вывода

| 1 1 1 0      |            |                  |  |

|--------------|------------|------------------|--|

| Код операции | Приказ на  | Адрес устройства |  |

| Тод операции | ввод-вывод | ввода-вывода     |  |

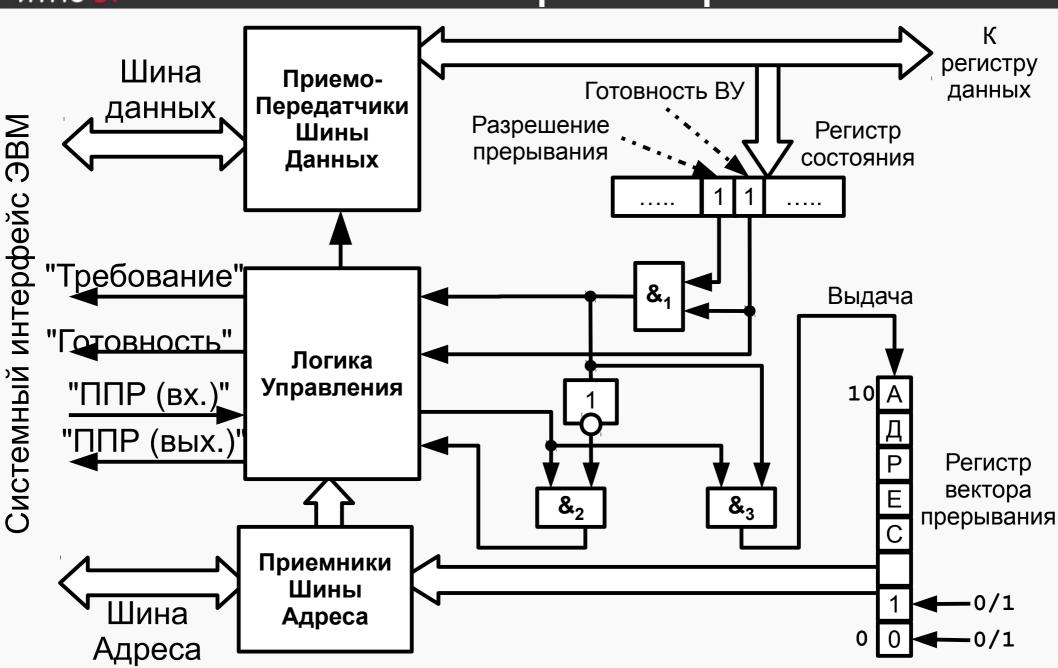

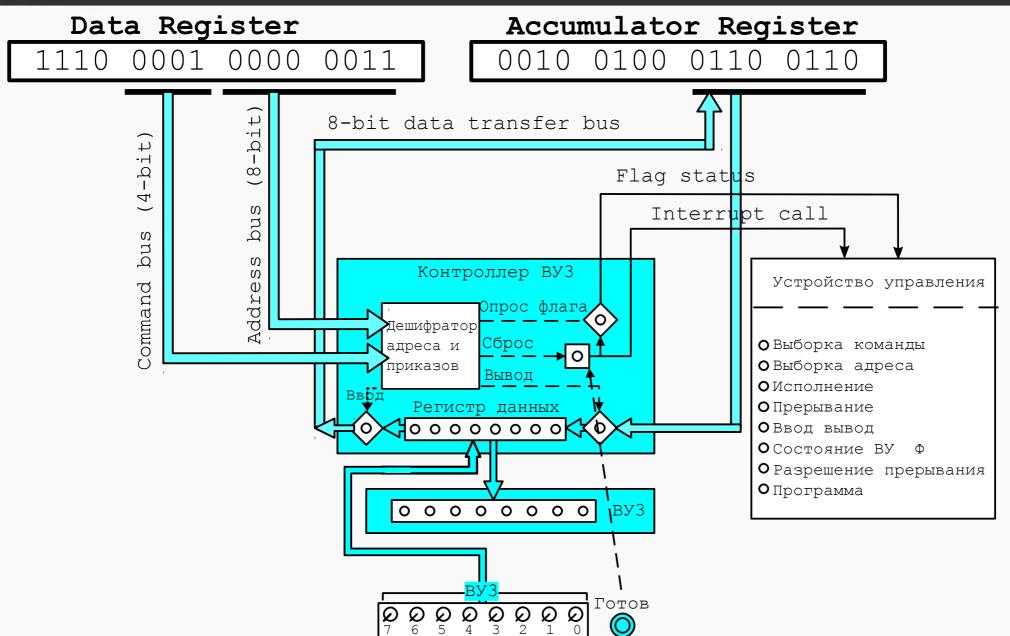

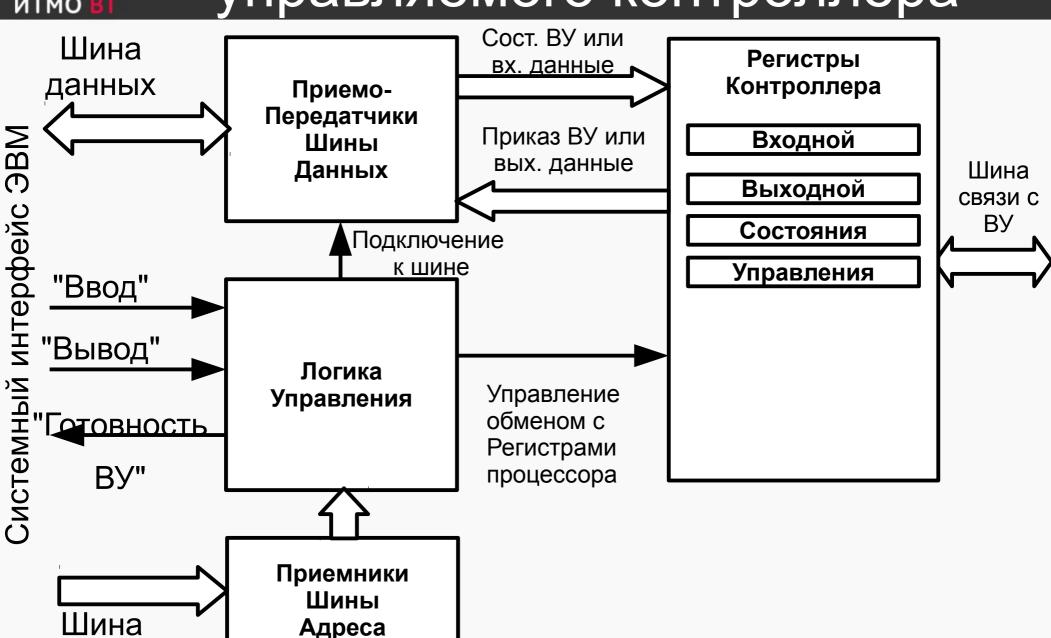

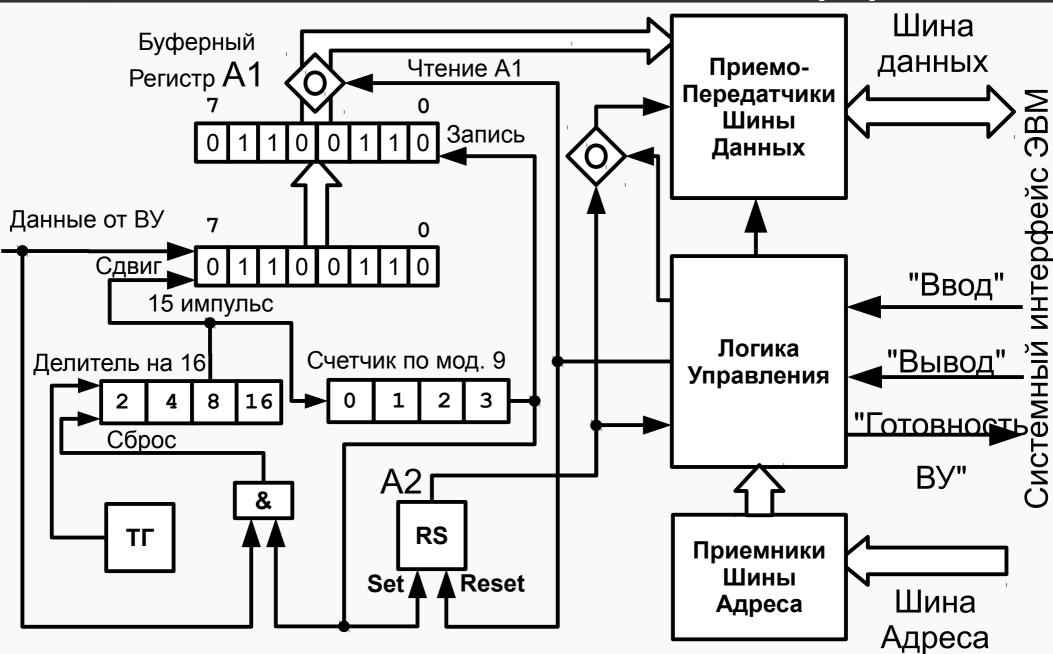

#### Device Controller

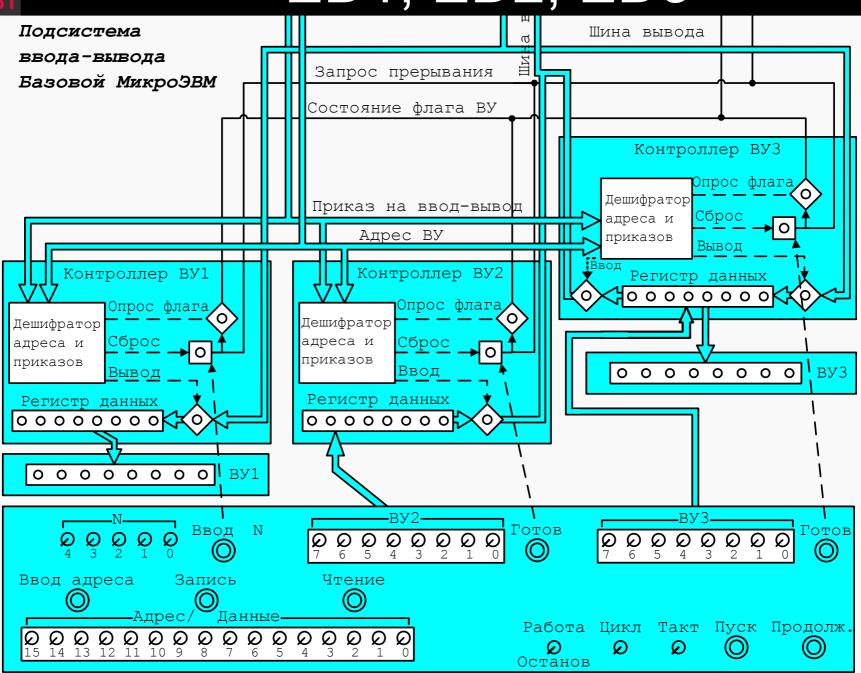

# Basic I/O Devices of the BComp: ED1, ED2, ED3

### Waiting for Input Cycle

|        |              | Enter tw | o symbols from the input device                                    |

|--------|--------------|----------|--------------------------------------------------------------------|

| ORG    | 005          |          |                                                                    |

| L8:    | WORD         | ·        | -8 number of shifts                                                |

| RES:   |              |          | Memory cell for the word "YES"                                     |

| ORG    | 020          | ;        | Address of the first instruction 020                               |

| BEGIN: | CLA          |          |                                                                    |

| SPIN1  | <b>→</b> TSF | 2 ;      | Waiting for the first symbol                                       |

|        | BR           | SPIN1 ;  |                                                                    |

|        | IN           | 2 ;      | Enter the first symbol                                             |

|        | CLF          | 2 ;      | Clear the flag. Able to enter the next symbol                      |

| RL:    | ROL          | ;        | Shift the first symbol                                             |

|        | ✓ISZ         | L8 ;     | High byte of the accumulator register                              |

|        | BR           | RL       |                                                                    |

| SPIN2: | TSF          | 2 ;      | Waiting for the second symbol                                      |

|        | BR           | SPIN2    |                                                                    |

|        | IN           | 2 ;      | Enter the 2nd symbol to low 8 bits of the A                        |

|        | CLF          | 2        |                                                                    |

|        | MOV          | RES <    |                                                                    |

|        | HLT          |          | How many instruction cycles will BComp wait for the second symbol? |

#### Time Costs

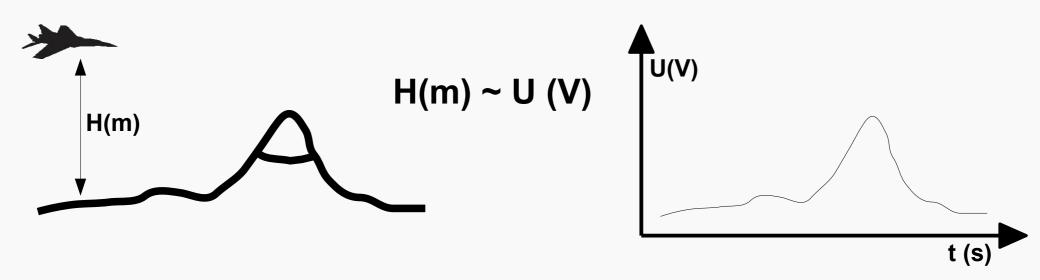

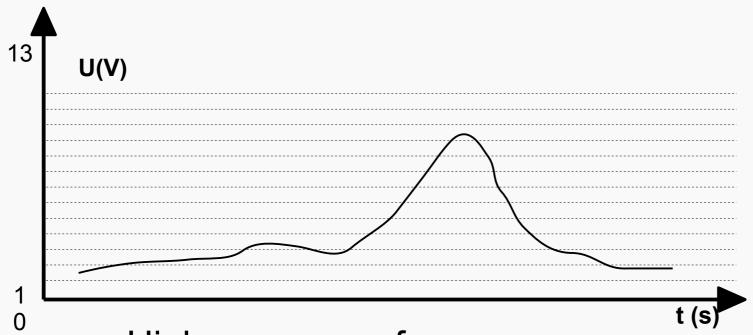

#### BComp ED0 Timer

- Sets ED readiness every (100 \* DR of ED content) ms:

- Shifted fixed decimal radix point

- If DR of ED value == 0 readiness won't set

- Could be used for asynchronous data exchange (How?)

#### BComp ED4 Text Printer

- Prints symbols from DR of ED in specified encoding

- Adjustable delay (print time) from 100 ms to 10 s

- Line break by CR symbol (0A<sub>16</sub>)

- NUL (0) clear sheet

- Another symbols unspecified behaviour

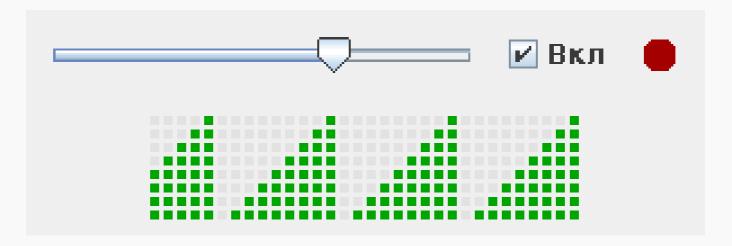

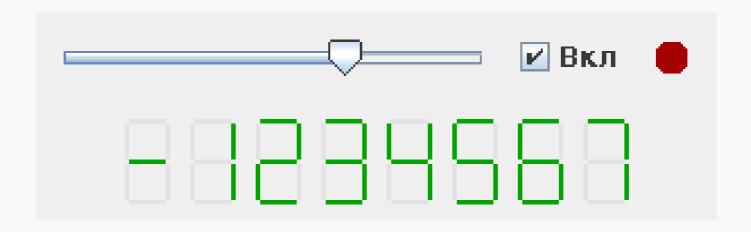

### BComp ED5 Ticker

- Screen matrix size: 32x8

- Shifts left on every new value in DR of ED

- New value appears on the right side of the screen

- Low bit is on the bottom

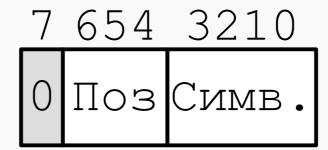

# БЭВМ: ВУ-6 8-ми разрядный семисегментный индикатор

• Формат РДВУ:

- Симв==(A<sub>16</sub>) установка в разряде знака «-»

- Симв==(B<sub>16</sub>-F<sub>16</sub>) сброс разряда

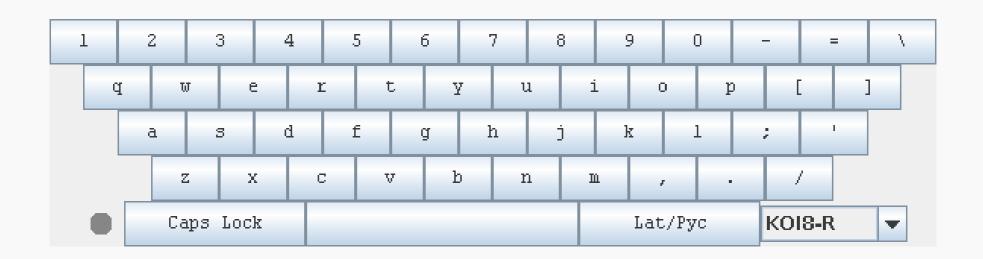

#### БЭВМ: ВУ-7 клавиатура

- Код нажатой клавиши в выбранной кодировке устанавливается в РДВУ

- Автоматически устанавливается готовность

# БЭВМ: ВУ-8 Цифровая клавиатура

- При нажатии клавиши ее код помещается в РДВУ

- Клавиша 0-9 код 0-9

- Клавиша «-» код А

- «+» код В

- «/» код С

- «\*» код D

- «.» код E

- «=» код F

| 7 | 8 | 9 | 1 |

|---|---|---|---|

| 4 | 5 | 6 | * |

| 1 | 2 | 3 | - |

| 0 |   | = | + |

#### БЭВМ: ВУ-9 БЭВМ

- Два стандартных контроллера ввода-вывода (как ВУ-3) связаны между собой

- IN читает информацию из РДВУ контроллера

- OUT записывает данные в РДВУ **обоих** контроллеров

- CLF одного контроллера приводит к установке флага связанного контроллера

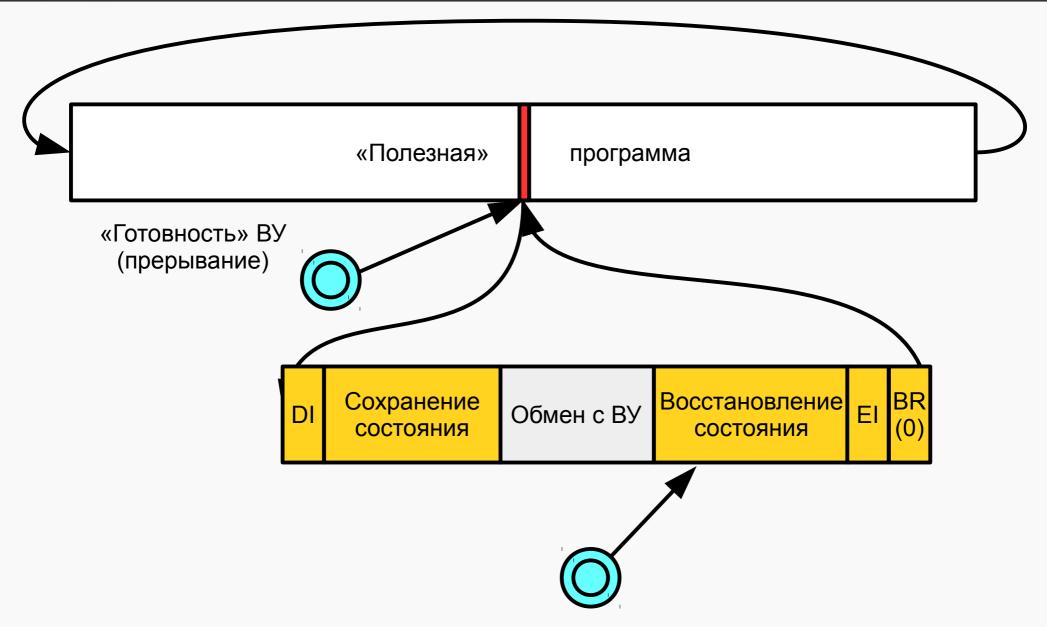

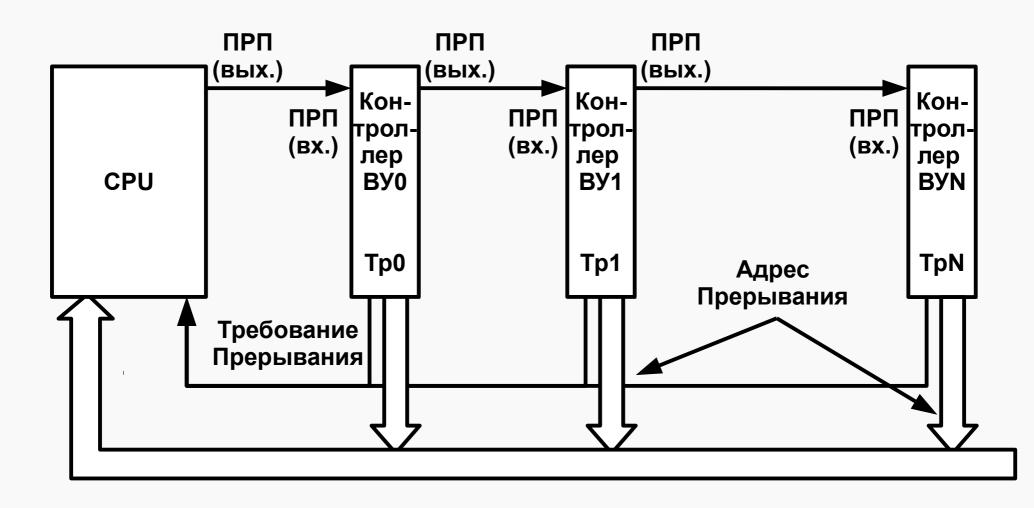

### Инициация обмена по прерыванию

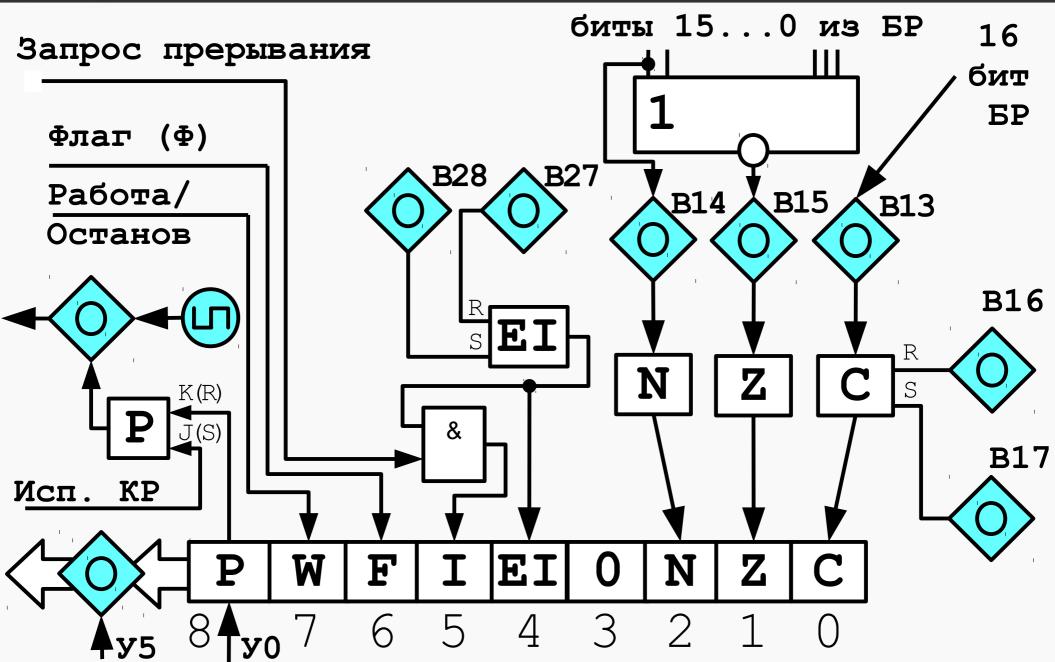

### Регистр состояния и команды

| Бит | Мнем. | Содержимое                                                                                   |  |  |  |  |

|-----|-------|----------------------------------------------------------------------------------------------|--|--|--|--|

| 0   | С     | Перенос                                                                                      |  |  |  |  |

| 1   | Z     | Нуль                                                                                         |  |  |  |  |

| 2   | N     | Знак                                                                                         |  |  |  |  |

| 3   | 0     | 0 - используется для организации безусловных переходов в МПУ                                 |  |  |  |  |

| 4   | EI    | Разрешение прерываний                                                                        |  |  |  |  |

| 5   | I     | Прерывание (логическое "И" шины запроса на прерывание и бита 4 РС – "разрешение прерываний") |  |  |  |  |

| 6   | F     | Состояние ВУ (Ф)                                                                             |  |  |  |  |

| 7   | W     | Состояние тумблеров РАБОТА/ОСТАНОВ (1 - РАБОТА)                                              |  |  |  |  |

| 8   | P     | Программа                                                                                    |  |  |  |  |

| Наименование          | Мнемон. | Код  | Описание                                 |

|-----------------------|---------|------|------------------------------------------|

| Разрешение прерываний | EI      | FA00 | Установка бита 4 (разрешение прерываний) |

| Запрещение прерываний | DI      | FB00 | Сброс в 0 бита 4 (разрешение прерываний) |

| Возврат из прерывания | BR (0)  | C800 | Переход по адресу, сохраненному в яч. 0  |

- После выполнения команды управление передается циклу прерывания

- Если бит 7 РС (Работа/Останов) == 0 то останов БЭВМ

- Если бит 5 РС (Прерывание) ==0 то переход к следующий команде (циклу выборки команды)

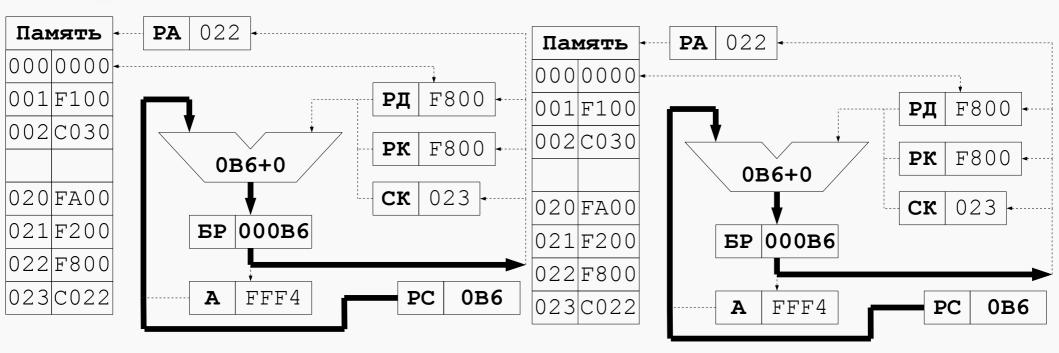

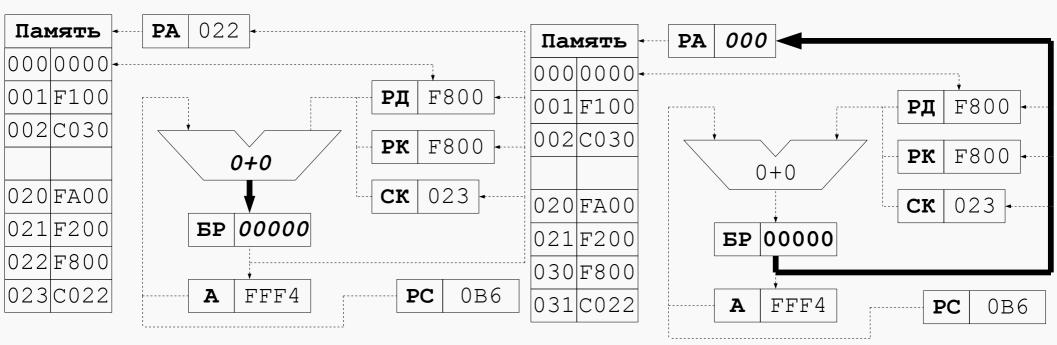

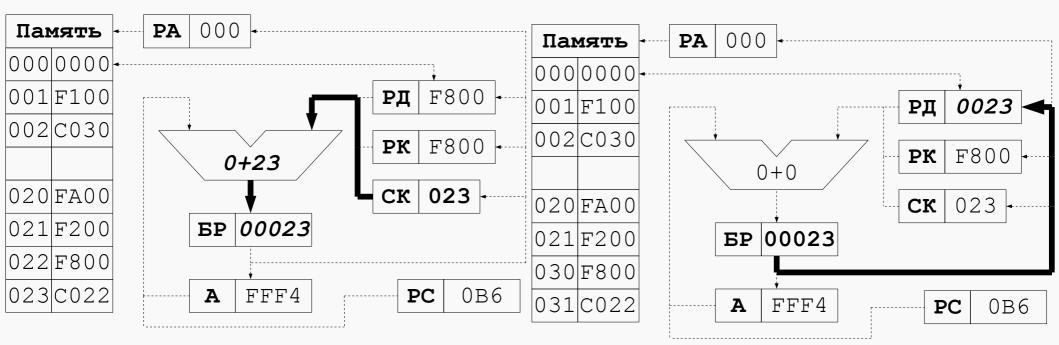

• 0 — (ячейка сохранения адреса возврата) записывается в РА

• Содержимое СК через БР переписывается в РД

- Содержимое РД записывается по адресу 0, тем самым обеспечивая возможность возврата из прерывания

- 1 записывается в БР и далее в СК, определяя первую исполняемую команду

- Производится запрещение прерываний в РС, сбрасывается бит 4 «разрешение прерываний», что приводит к сбросу бита 5 «прерывание» (В->8)

- После этого переход к циклу выборки команды из ячейки 1, т.е. обработке прерывания

# После каких команд нет цикла прерывания?

- DI

- Нет необходимости. Прерывания запрещены

- HLT

- Нет необходимости. Программа остановлена

- EI

- Приведет к зацикливанию обработчика прерывания Завершение обработчика:

```

EI

BR (0)

```

# Обработка прерываний: Основная программа

```

Обработка прерываний

```

Готовность ВУ1: 2\*А→РДВУ1, Готовность ВУ3: РДВУ3→ яч.29

ORG 000

**RET: WORD ?** ; Ячейка адреса возврата

**NOP** ; Ячейка отладочной точки

; останова (NOP/HLT)

**BR INT** ; Переход к обработке прерываний

**ORG 020 ;** Основная программа

**BEGIN: EI** ; Установка состояния разрешения прерывания

**СLA** ; Первоначальная очистка аккумулятора

**LOOP:** ; Цикл для наращивания

**BR LOOP** ; содержимого аккумулятора

ORG 029 ; Ячейка для хранения кодов,

**IO3: WORD ?** ; поступающих с ВУ-3

### Обработка прерываний: Сохранение и восстановление

```

Готовность ВУ1: 2*А→РДВУ1, Готовность ВУ3: РДВУ3→ яч.29

030

ORG

INT:

MOV SAVED A ; Сохранение содержимого А и С

ROL

MOV SAVED C

Основная программа обработки прерывания

(см. следующий слайд)

RESTORE: NOP

; отладочная точка останова (NOP/HLT)

CLA

; Восстановление содержимого С и А

ADD SAVED C

ROR

CTA

CMA

AND SAVED A

ΕI

; Возобновление состояния

; разрешения прерывания

BR (RET) ; Возврат из обработки прерывания

SAVED A: WORD ?

SAVED C: WORD ?

```

# Обработка прерываний: Прерывание

```

Готовность ВУ1: 2*А→РДВУ1, Готовность ВУ3: РДВУ3→ яч.29

TSF 3

; Опрос флага ВУ-3

BR CHECK1 ; Если сброшен \rightarrow к опросу флага ВУ-1

BR READY3 ; Переход на ввод данных из ВУ-3

CHECK1: TSF 1 ; Опрос флага ВУ-1

BR READY2 ; Если сброшен \rightarrow к опросу флага ВУ-2

BR READY1 ; Переход на вывод данных в ВУ-1

READY3: CLA

; Ввод данных из ВУ-3

IN 3

CLF 3

; Сброс флага ВУ-3

MOV IO3

; Пересылка значения в ячейку 29

BR RESTORE

READY1: CLA

ADD SAVED A

ROL

OUT 1 ; Вывод на ВУ-1 8-ми

CLF 1

; Сброс флага ВУ-1

BR RESTORE

READY2: CLF 2

```

### Ввод-вывод

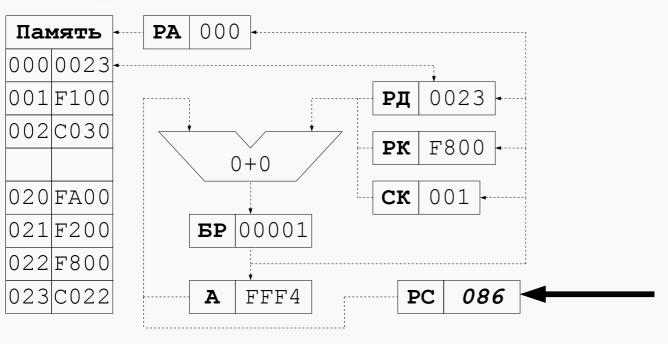

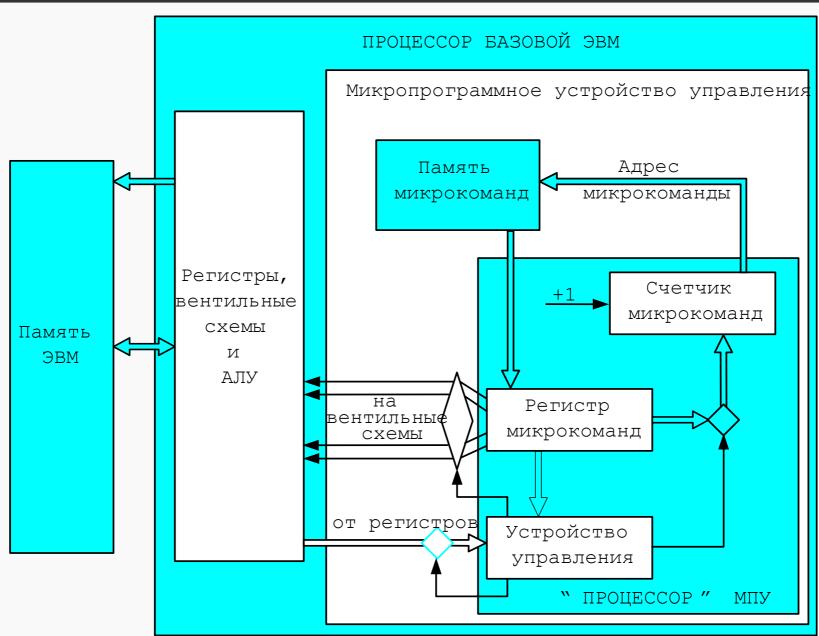

# Микропрограммное устройство управления

8

#### Многоуровневая ЭВМ

Уровень программых систем (специальный язык) Уровень проблемно-ориентированных задач (один из алгоритмических языков) Язык Ассемблера Машинные команды Микропрограммный Уровень

#### МПУ

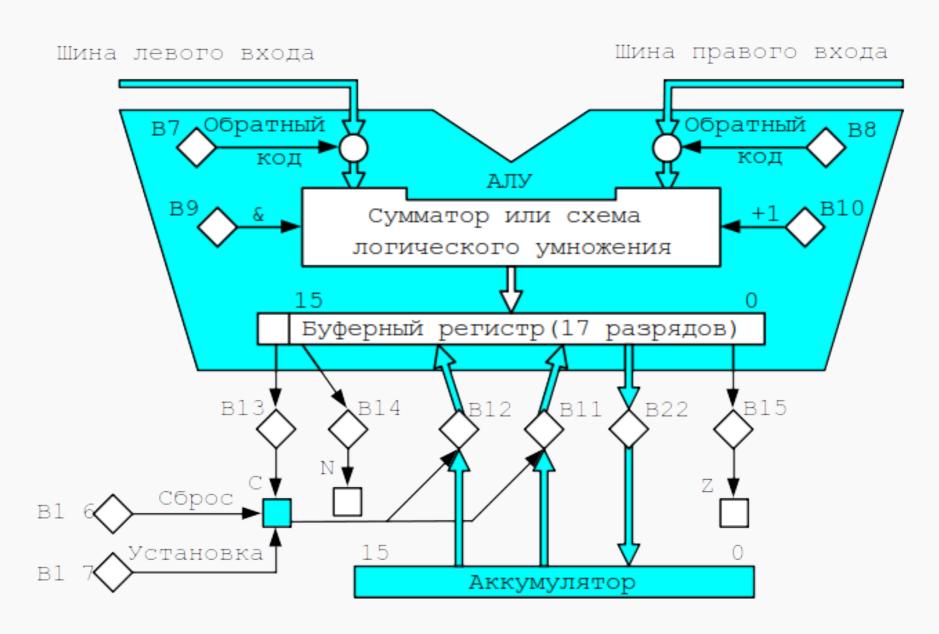

#### АЛУ

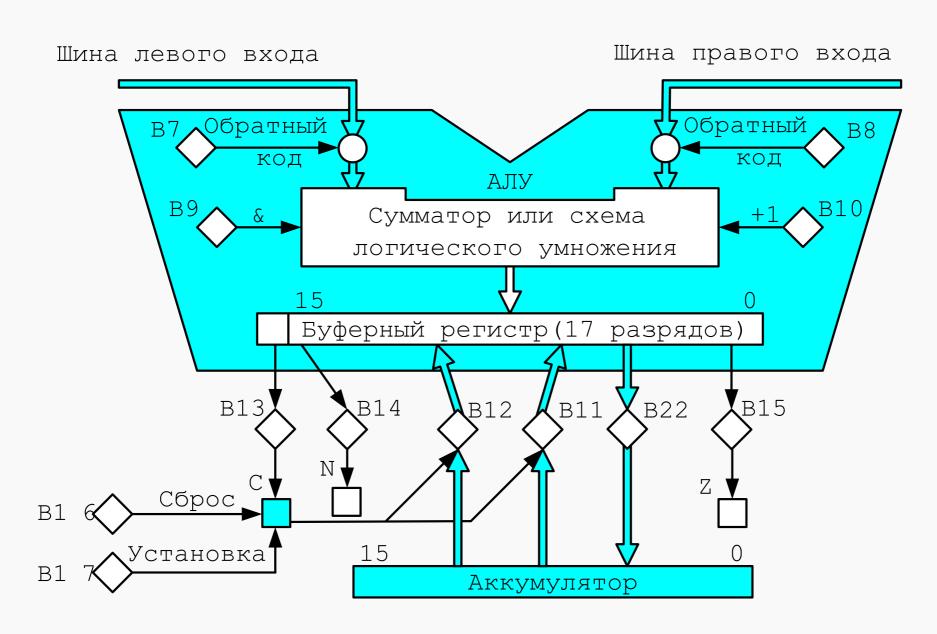

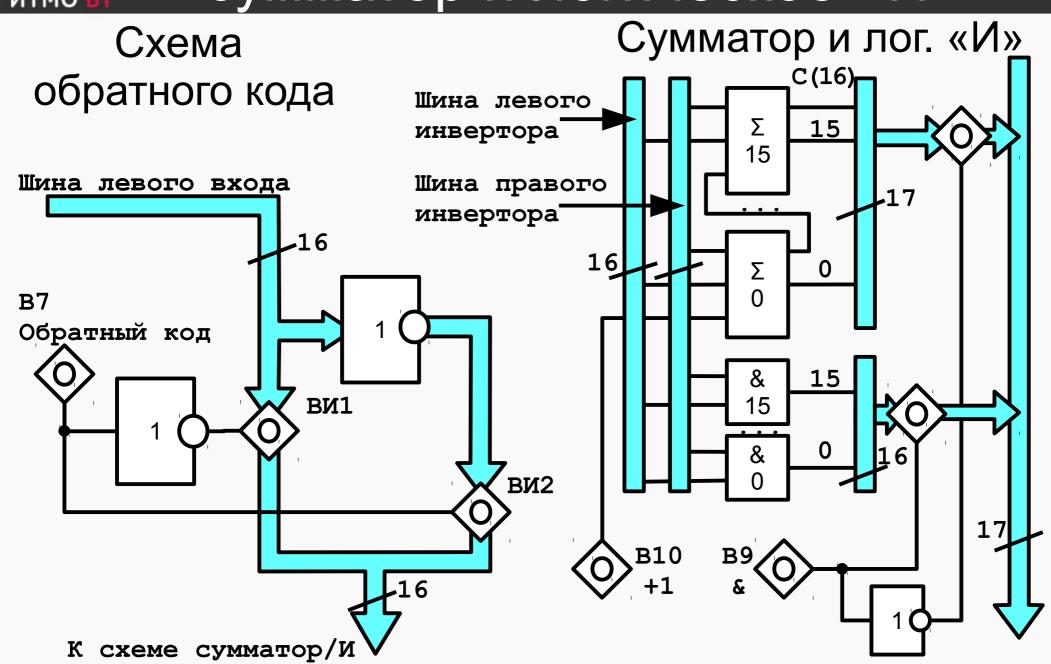

# АЛУ: Обратный код, сумматор и логическое «И»

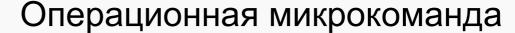

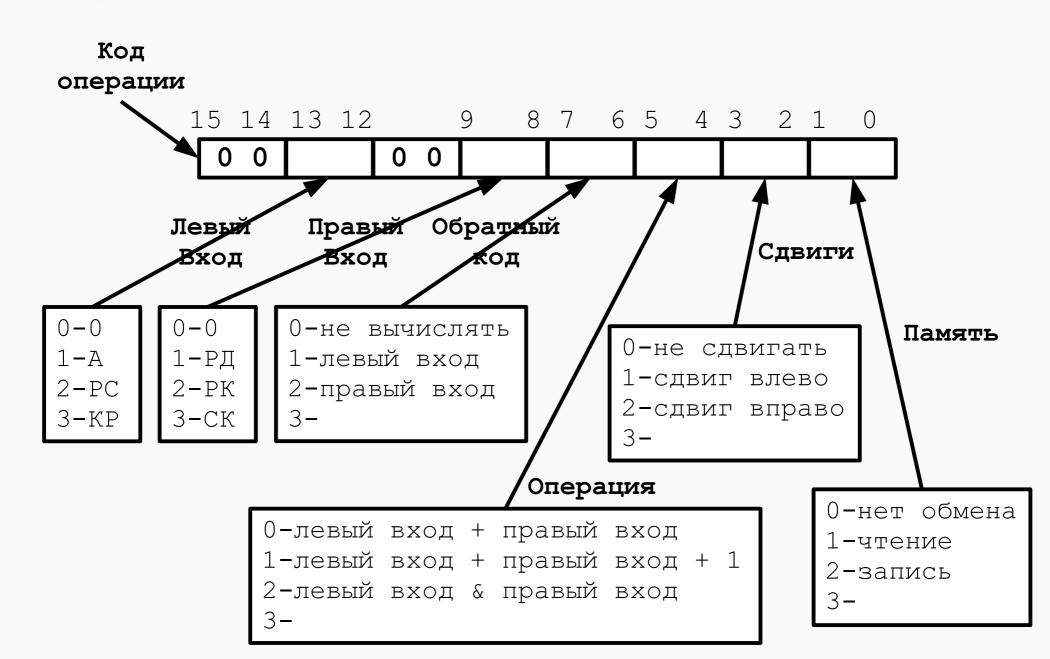

### Горизонтальные микрокоманды

Поле выбора проверяемого бита

#### МПУ

## Регистр состояния

#### Вентильные схемы

- Входные сигналы на входы АЛУ

- В1-В3 левый вход АЛУ

- В4-В6 правый вход АЛУ

- Арифметические операции и сдвиги

- B7-B12

- Установка признаков

- B13-B22

- Работа с памятью

- B23-B24

- Организация ввода-вывода информации

- B25-B28

- Останов ЭВМ В0

### Интерпретатор БЭВМ

- 256 ячеек для хранения микрокоманд, включая резерв

- Содержит вертикальные микрокоманды (см. далее)

- Оформлено в виде таблицы (см. Методу!)

| Ад-<br>pec | Микрокоманды   |              | Коментарии |                      |

|------------|----------------|--------------|------------|----------------------|

|            | Горизонтальная | Вертикальная | Метка      | Действие             |

| 01         | 0000 0008      | 0300         | НАЧ        | СК→БР                |

| 02         | 0004 0000      | 4001         |            | БР→РА                |

| 03         | 0080 0408      | 0311         |            | ОП (РА) →РД, СК+1→БР |

## Интерпретатор БЭВМ

- Цикл выборки команд

- Цикл выборки адреса операнда

- Цикл исполнения адресных команд

- Декодирование адресных команд

- Исполнение адресных команд

- Декодирование и исполнение безадресных команд

- Декодирование и исполнение команд ввода-вывода

- Цикл прерывания

- Пультовые операции

- Свободные ячейки для:

- Арифметической команды

- Команды перехода

- Безадресной команды

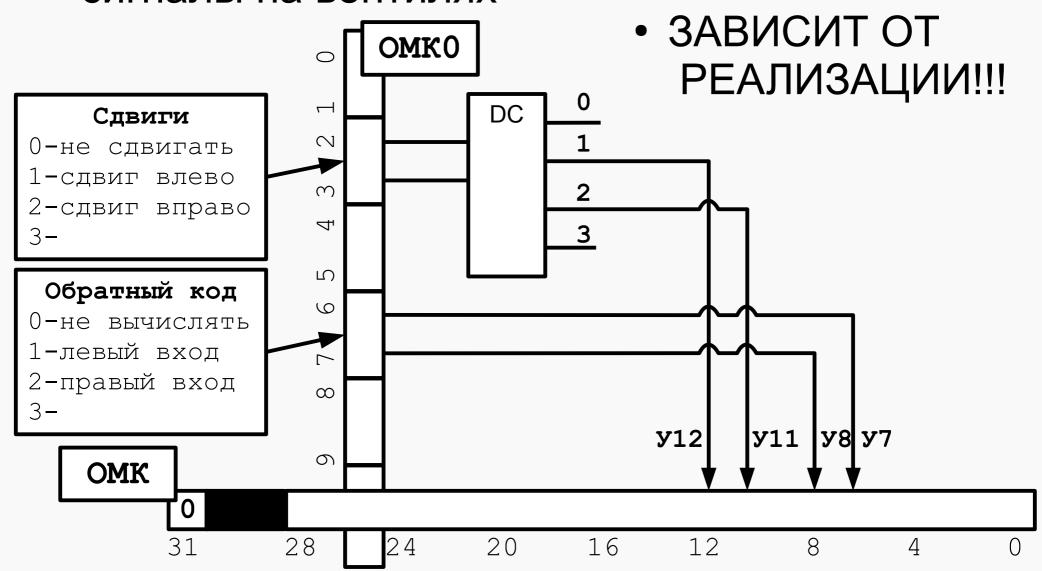

# Вертикальные микрокоманды: ОМКО

### Вертикальные микрокоманды: ОМК1

# Вертикальные микрокоманды: УМК

# Преобразование вертикальных микрокоманд в горизонтальные

• Задача — преобразовать коды в управляющие сигналы на вентилях

# С БЭВМ — все!!!!

# История и Архитектуры ЭВМ

9

# итмо вт

## История

- Нулевое поколение механические компьютеры (1642–1945)

- Налоговый сумматор (Паскаль), калькулятор на 4 действия (Лейбниц)

- Первое поколение электронные лампы (1945–1955)

- COLOSSUS (1943, Тьюринг), ENIAC (1946, Моушли), IAS (1951, фон Нейман)

- Второе поколение транзисторы (1955–1965)

- TX-0 (1955, МТИ), PDP-1 (1961, DEC), PDP-8, 7090 (IBM), 6600 (1964, CDC)

- Третье поколение интегральные схемы (1965–1980)

- Семейство System/360 (1965, IBM), PDP-11 (1970, DEC)

- Четвертое поколение сверхбольшие интегральные схемы (1980–?)

- IBM PC (1981), Apple, Intel, IBM, Dec, Compaq, HP, Sun...

- Пятое поколение небольшие и «невидимые» компьютеры (1989-?)

#### История в СССР/России

- Первое поколение электронные лампы

- Лебедев, 1950, МЭСМ

- БЭСМ, 1953, БЭСМ 10000 oп/c, 53КВТ.

- Второе поколение транзисторы

- 5Э92б, 1964, самодиагностика, горячая замена, 500000 оп/с

- БЭСМ-6, 1965 год, +ковейерная обработка, удаленное управление по телеф. Линиями

- Третье поколение интегральные схемы

- Директива «Ряд», 1968 год, клонирование S/360, 1971 год ЕС ЭВМ

- Клоны PDP-11

- Четвертое поколение сверхбольшие интегральные схемы

- Эльбрус разработка по настоящее время

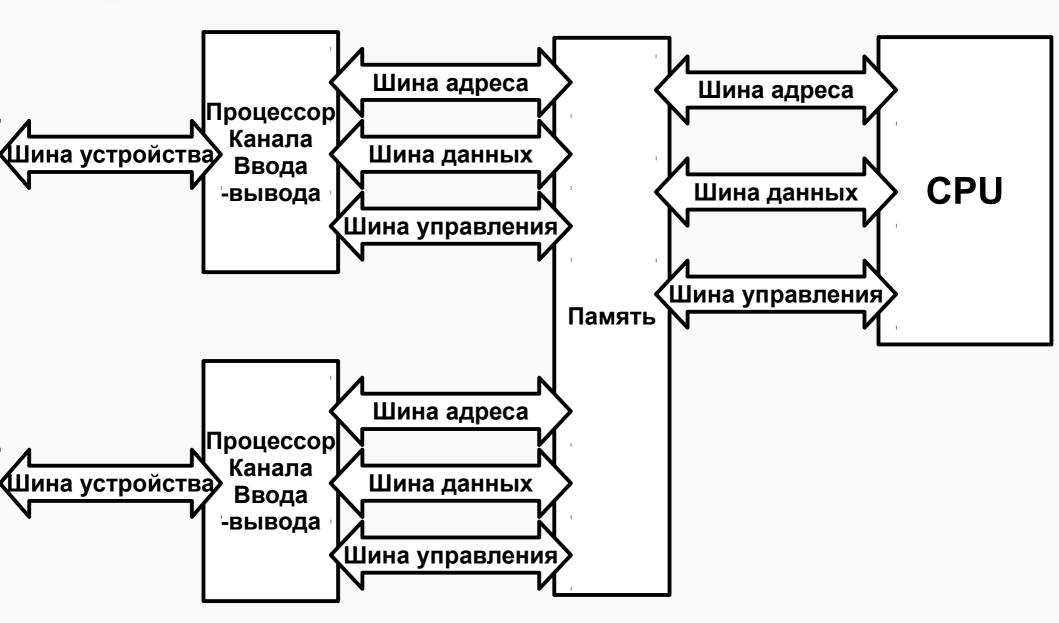

# Канальная организация

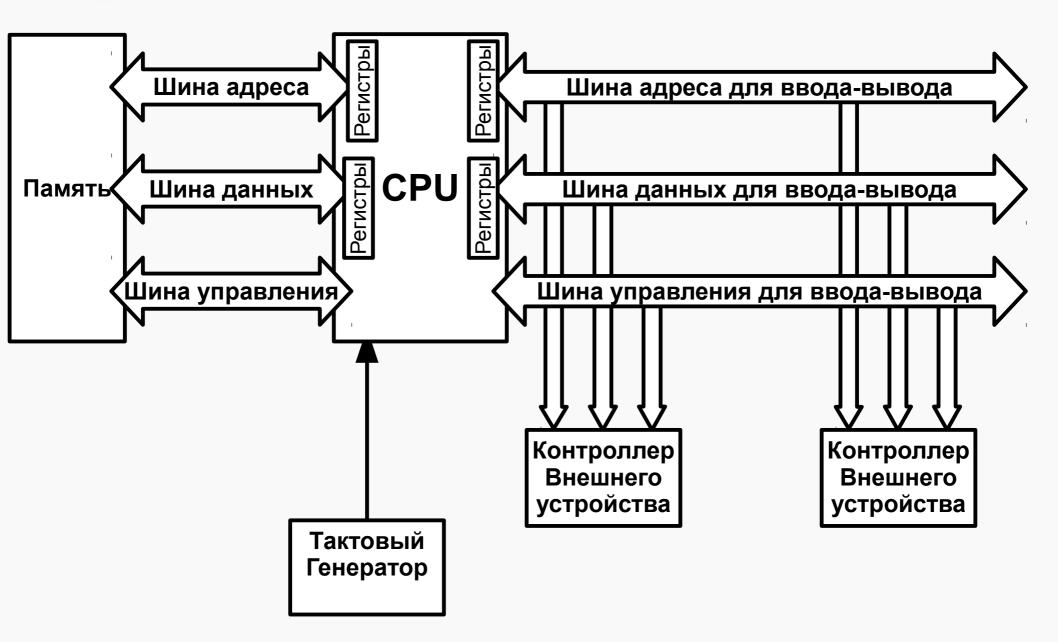

#### Раздельные шины

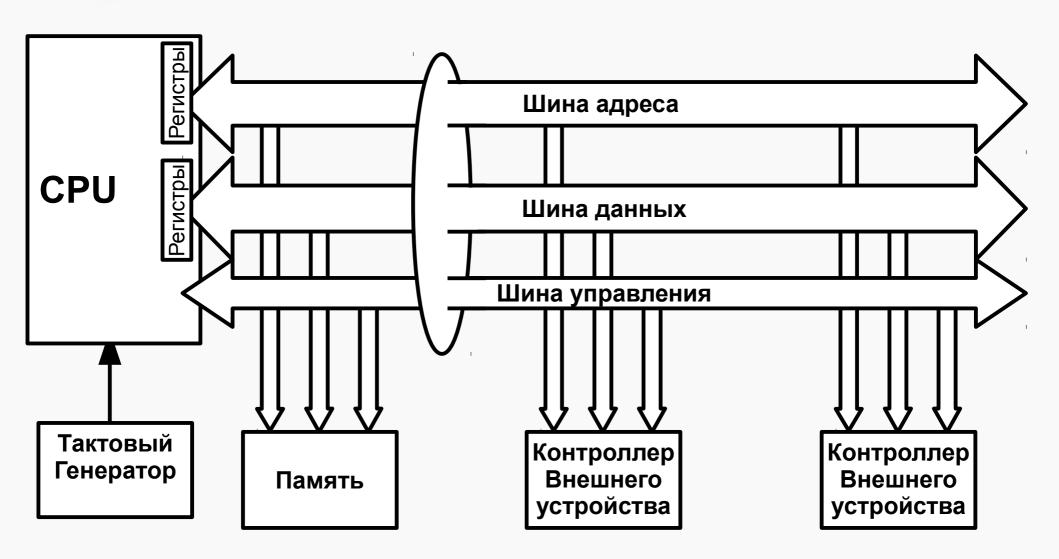

# Общие шины

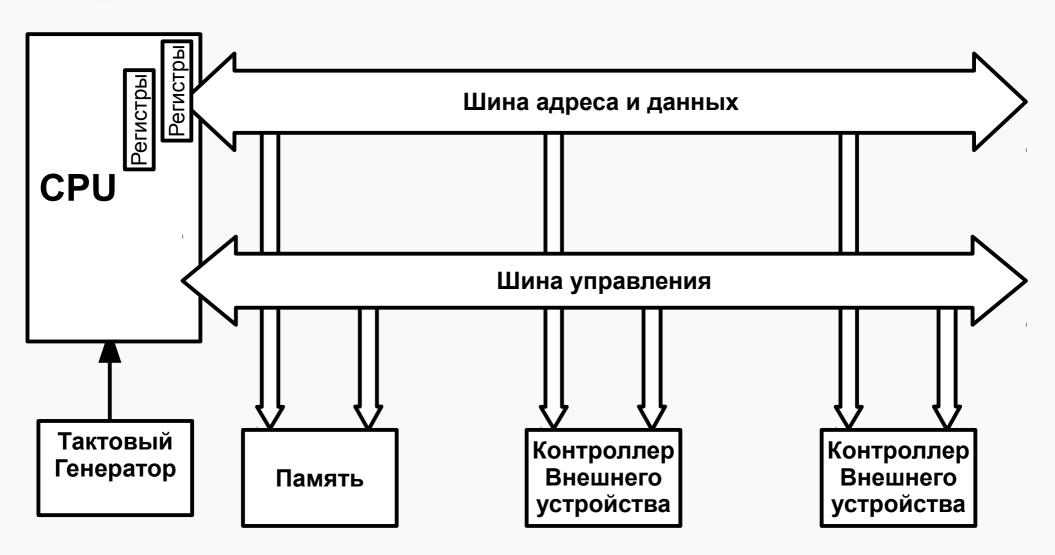

# Мультиплексирование шин

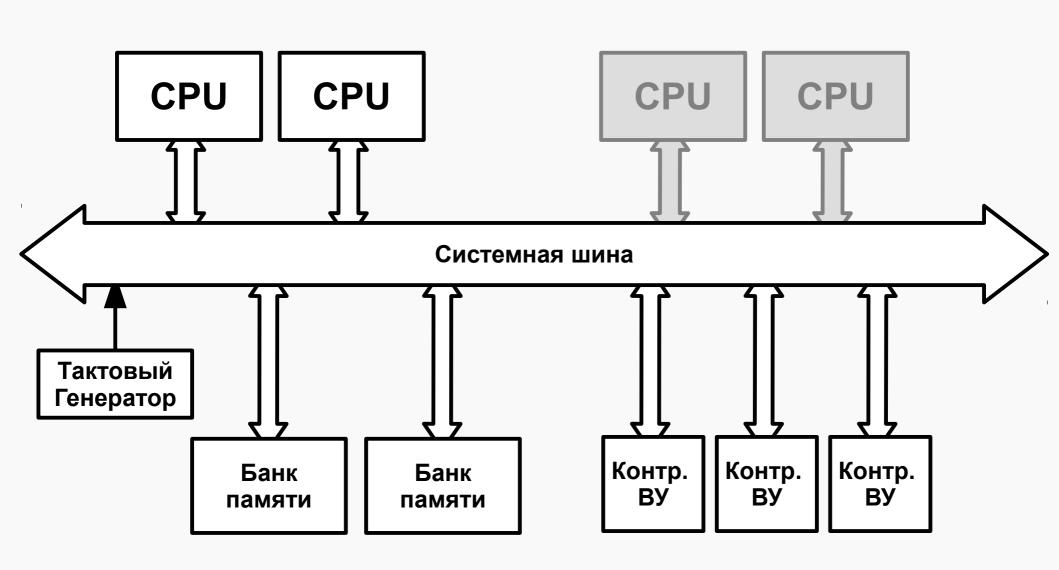

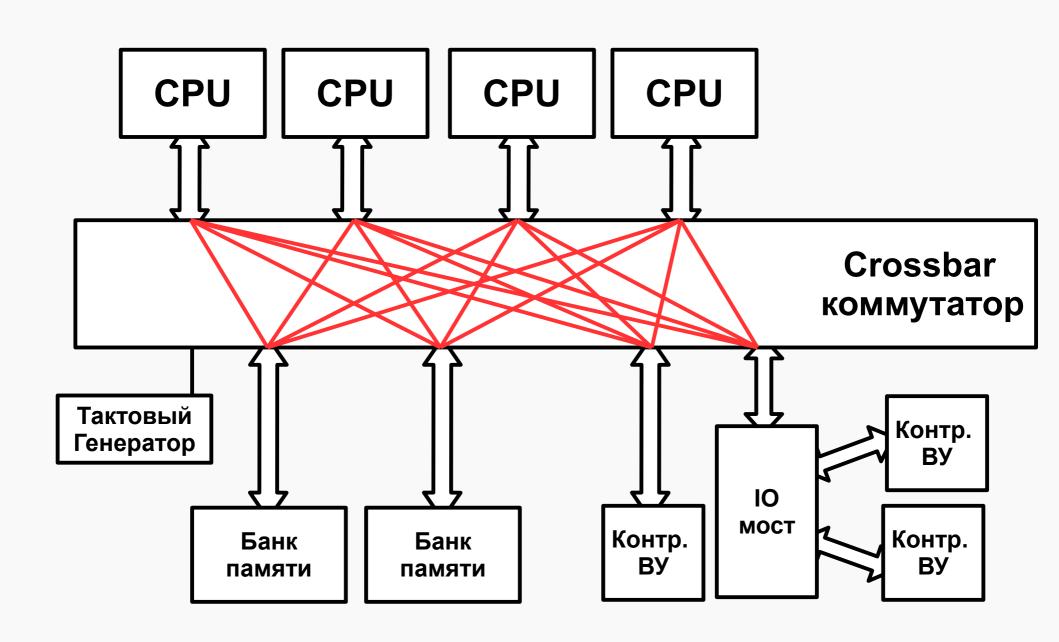

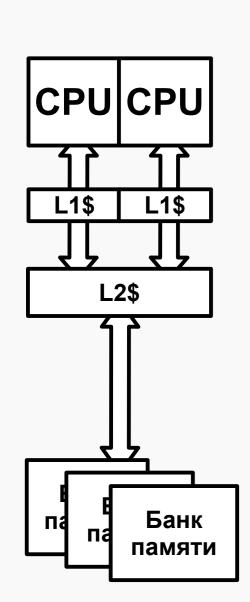

# Мультипроцессорность: UMA - Uniform Memory Access

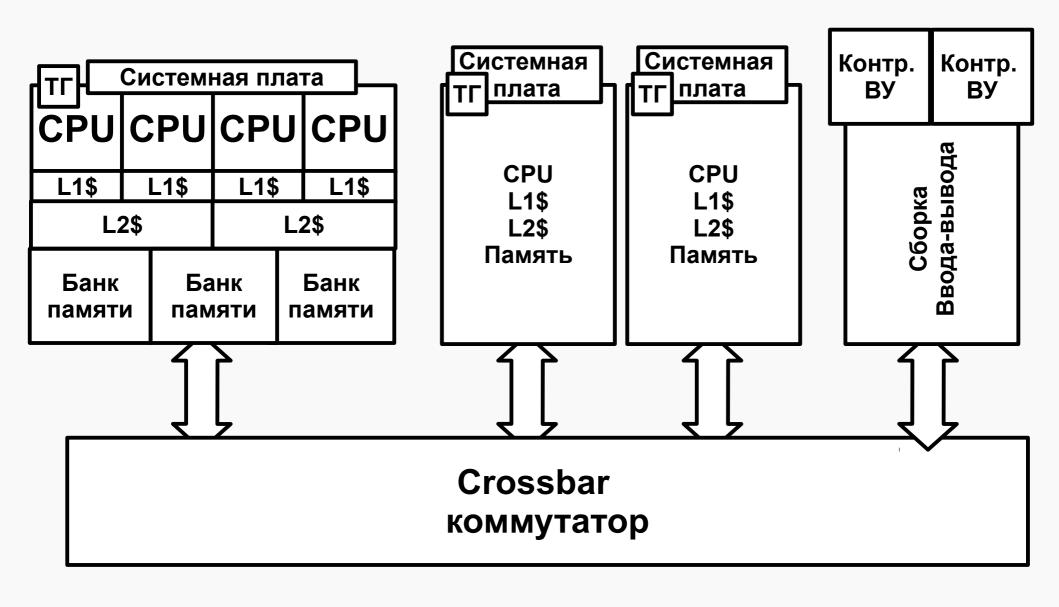

# Мультипроцессорность: Коммутатор

# Мультипроцессорность: NUMA Non-Uniform Memory Access

# Современные коммерческие процессоры

- Разрядность адреса и данных 16/32/64 бита

- Тактовые частоты 500МГЦ-5Ггц.

- Многопроцессорные 1-100+ CPU

- Многоядерные 1-16 ядер

- От 1 ГБ до терабайтов ОЗУ

- Используют кэш-память разных уровней

- Суперскалярные

- CISC, RISC, VLIW

## CISC, RISC, VLIW

- Complex Instruction Set Computer

- Традиционные процессоры (например Intel), отягощенные совместимостью

- Reduced Instruction Set Computer

- Простой набор инструкций, выполнение инструкции за такт

- Very Long Instructions Word

- Несколько инструкций, упакованных в одну команду

- Упаковка операций в инструкцию ложится на компилятор

# «Современные» процессоры Intel

| Year | Microarchitecture    | Pipeline stages                  | max. Clock   |

|------|----------------------|----------------------------------|--------------|

| 1989 | 486 (80486)          | 3                                | 100 MHz      |

| 1993 | P5 (Pentium)         | 5                                | 300 MHz      |

| 1995 | P6 (Pentium II)      | 14 (17 with load & store/retire) | 450 MHz      |

| 1999 | P6 (Pentium III)     | 12 (15 with load & store/retire) | 450~1400 MHz |

| 2000 | NetBurst (Pentium 4) | 20                               | 800~3466 MHz |

| 2003 | Pentium M            | 10 (12 with fetch/retire)        | 400~1000 MHz |

| 2004 | Prescott             | 31                               | 3800 MHz     |

| 2006 | Intel Core           | 12 (14 with fetch/retire)        | 3000 MHz     |

| 2008 | Nehalem              | 20                               | 3000 MHz     |

| 2008 | Bonnell              | 16 (20 with prediction miss)     | 2100 MHz     |

| 2011 | Sandy Bridge         | 14 (16 with fetch/retire)        | 4000 MHz     |

| 2013 | Silvermon            | 14-17 (16-19 with fetch/retire)  | 2670 MHz     |

| 2013 | Haswell              | 14 (16 with fetch/retire)        | ≈4000 MHz    |

| 2015 | Skylake              | 14 (16 with fetch/retire)        | ≈4000 MHz    |

| 2016 | Kaby Lake            | 14 (16 with fetch/retire)        | 4500 MHz     |

| 2017 | Coffe Lake           | 14 (16 with fetch/retire)        | 4700 MHz     |

| 2018 | Cannon Lake          |                                  |              |

https://en.wikipedia.org/wiki/List\_of\_Intel\_CPU\_microarchitectures

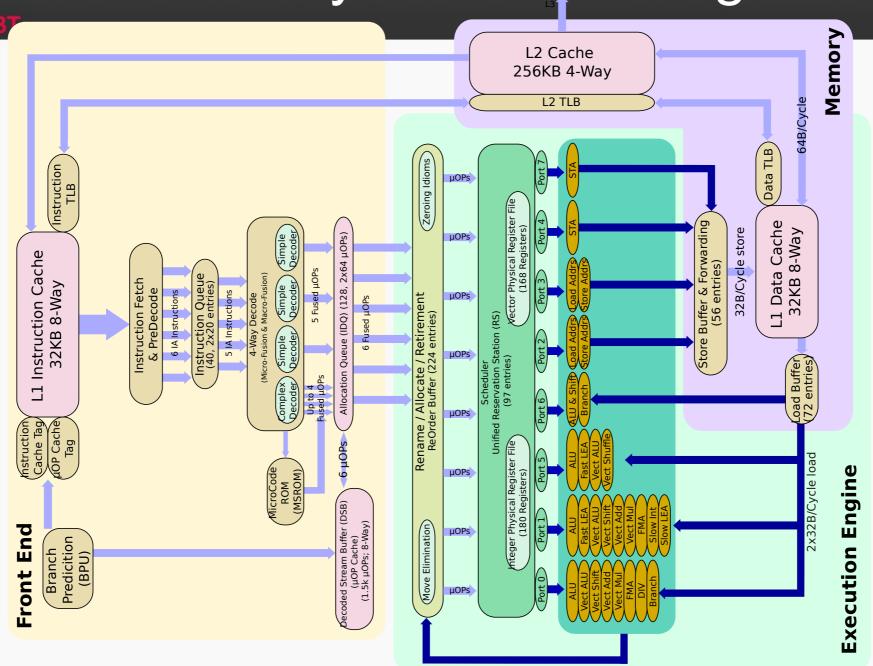

# Intel Skylake block diagram

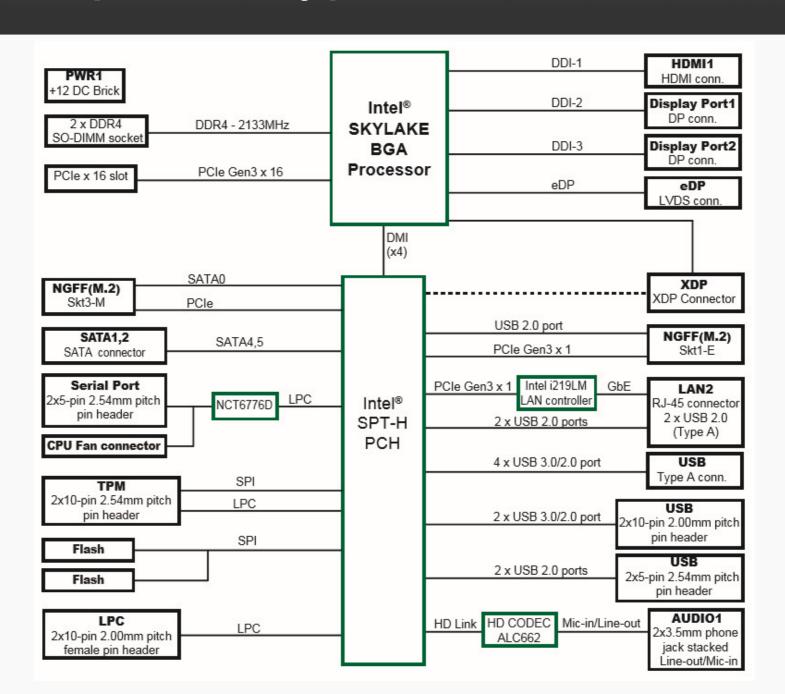

### Арихтектура: Arbor ITX-i89H

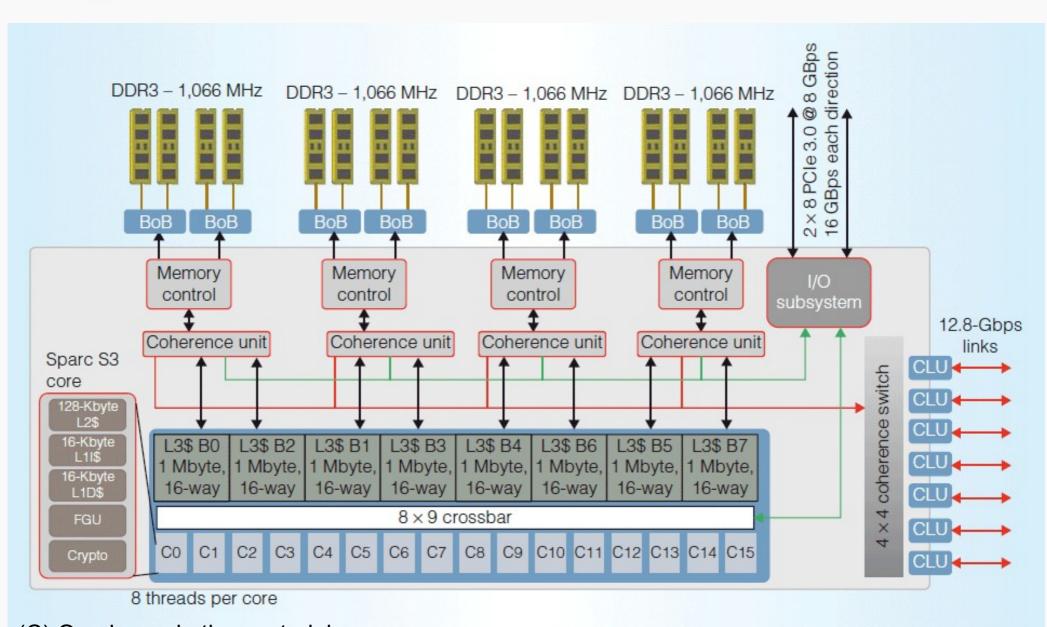

#### SPARC T5 16xCores

(C) Oracle marketing material

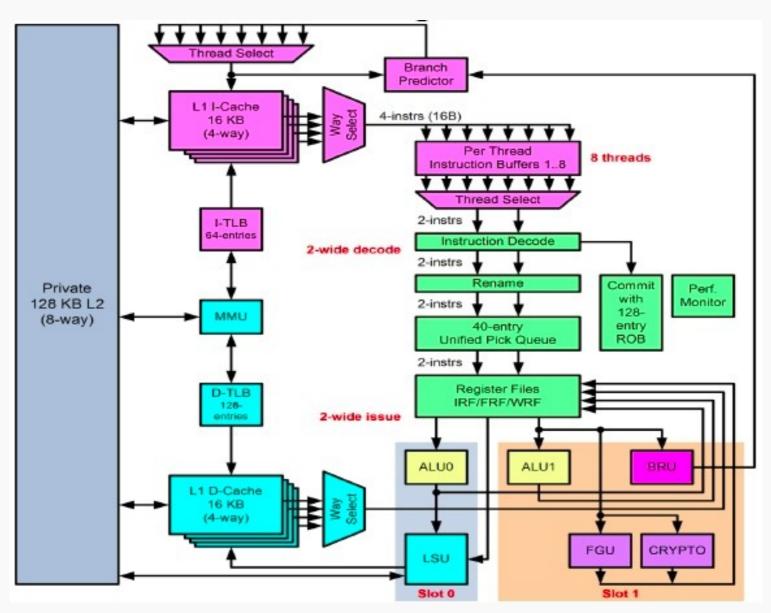

# Sparc S3 Core

http://www.theregister.co.uk/2011/08/22/

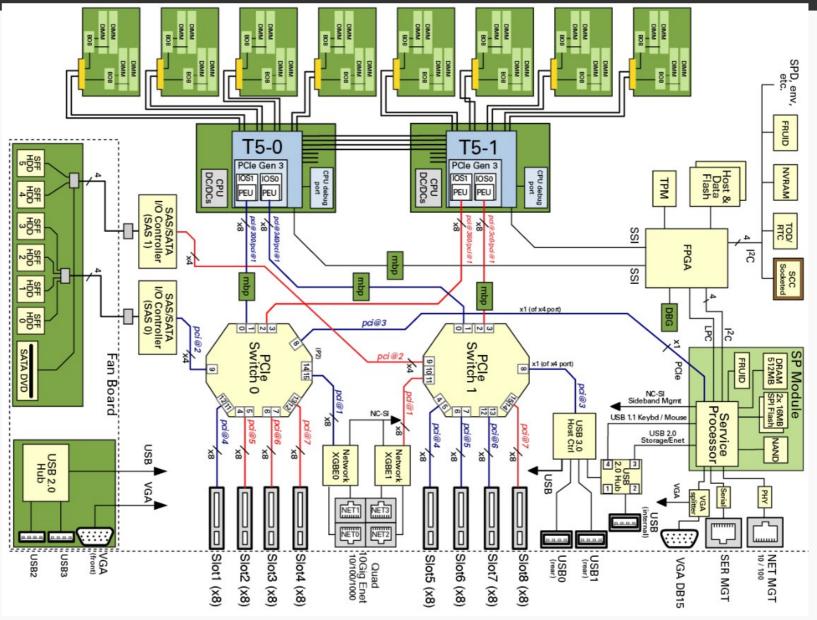

# Двухпроцессорная система на базе SPARC-T5

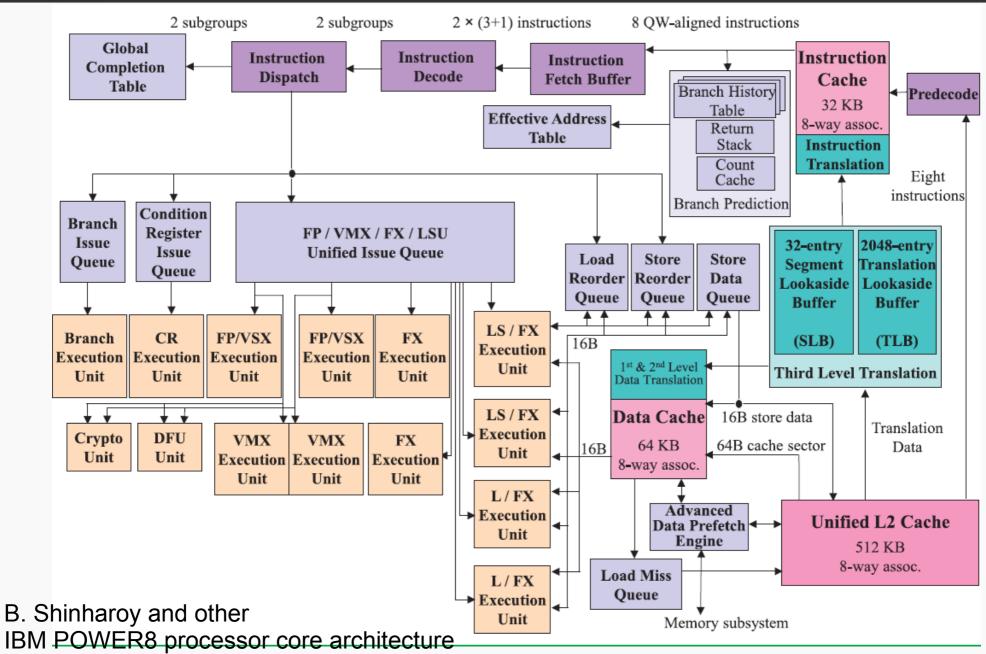

#### **IBM POWER8**

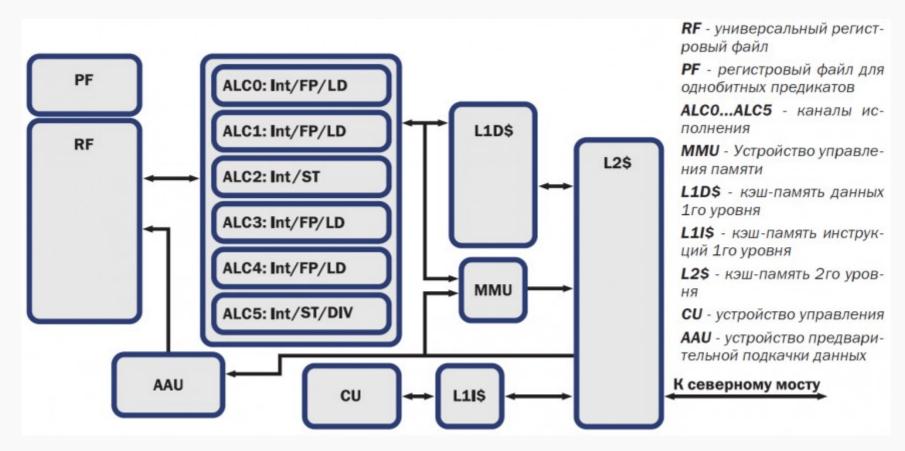

## Эльбрус 8с

- Технология 28нм

- 8 ядер х 1300МГц

- L1 I128K + D64K

- L2 512 K

- L3 16Мб

- 3-х канальная DDR3-1600MHZ

- До 80 BT

- Linux 2.2

- Эмуляция х86 (-30%)

http://www.mcst.ru/elbrus-8c

## Устройства хранения данных

10

### Характеристики памяти

- Месторасположение

- процессорные, внутренние, внешние

- Емкость

- В метрических (Кило-) и двоичных (Киби-) множителях

- Единица пересылки

- Слово, строка кэша, блок на диске

- Метод доступа

- Произвольный (адресный), ориентированных на записи (прямой), последовательный, ассоциативный

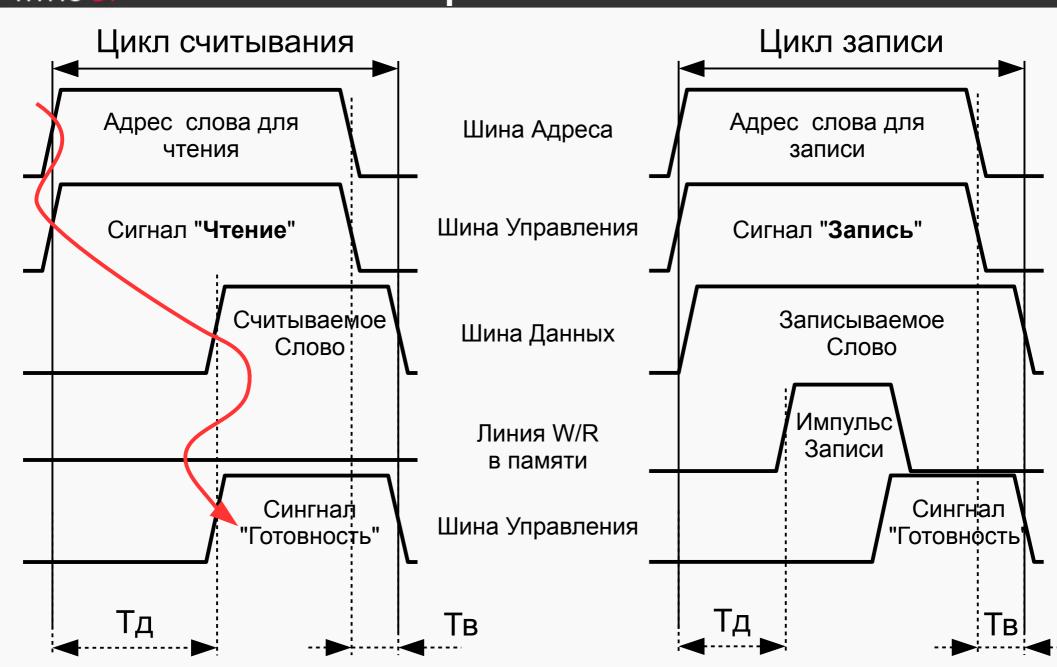

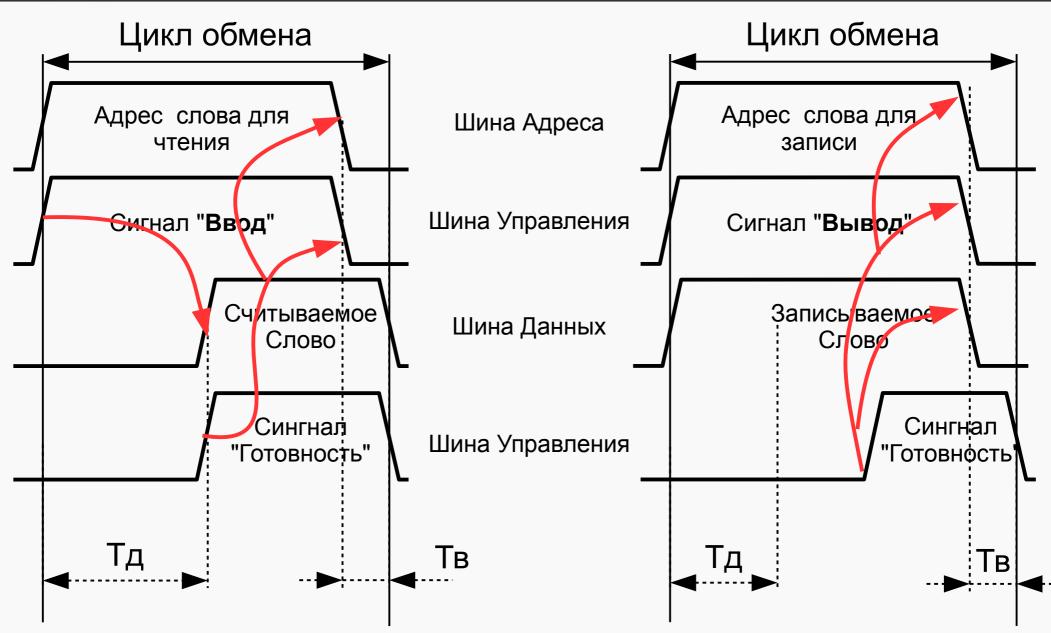

#### Характеристики памяти

- Быстродействие и временные соотношения

- Время доступа Тд

- Длительность цикла памяти (время обращения)

Тц

- Время чтения и время записи

- Время восстановления Тв

- Скорость передачи информации

- Физический тип и особенности

- Стоимость

#### Статическая vs Динамическая

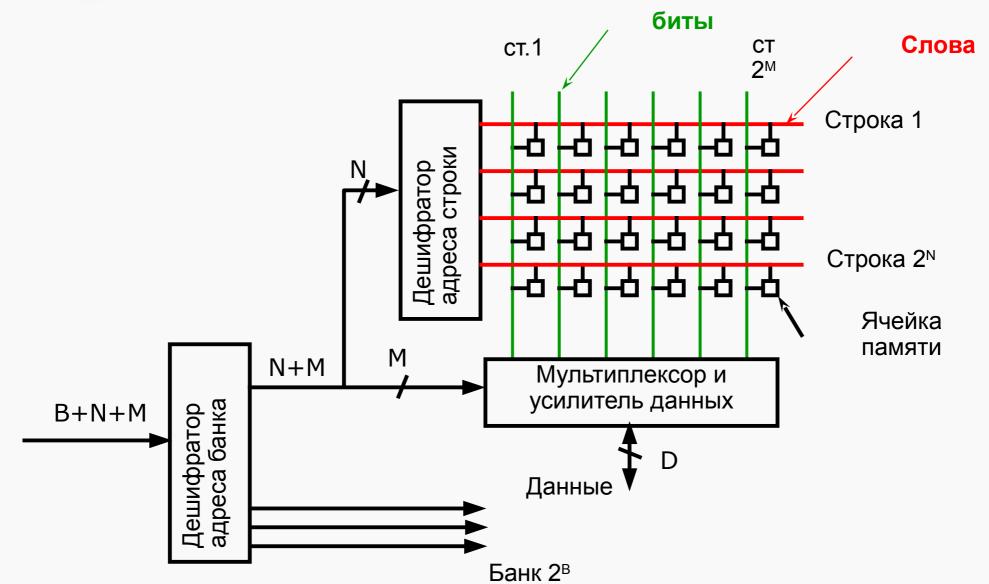

#### Адресуемая память

## Диаграммы работы с адресуемой асинхронной памятью

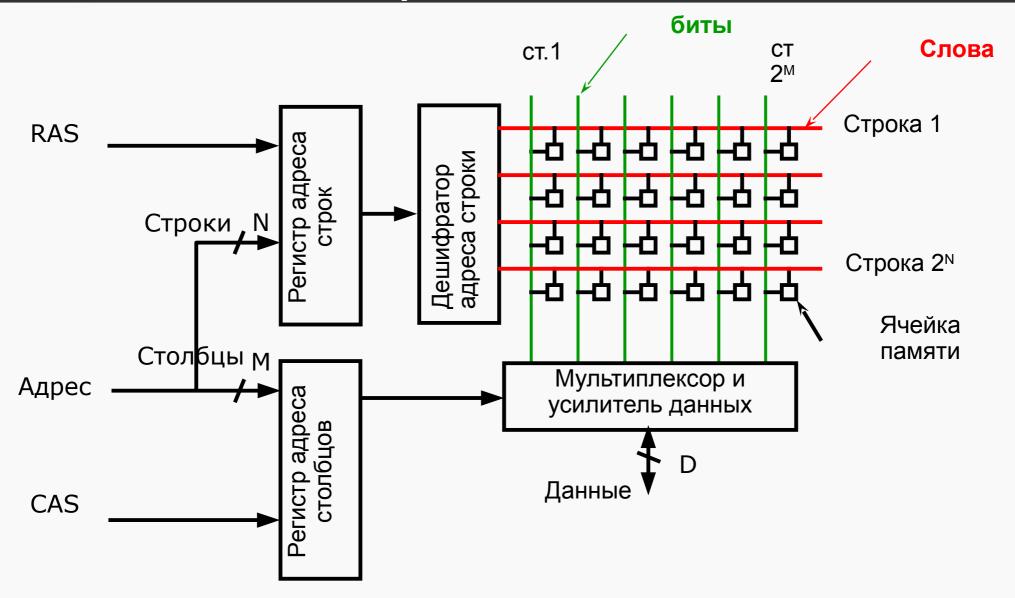

### Адресуемая память с фиксацией строк и столбцов

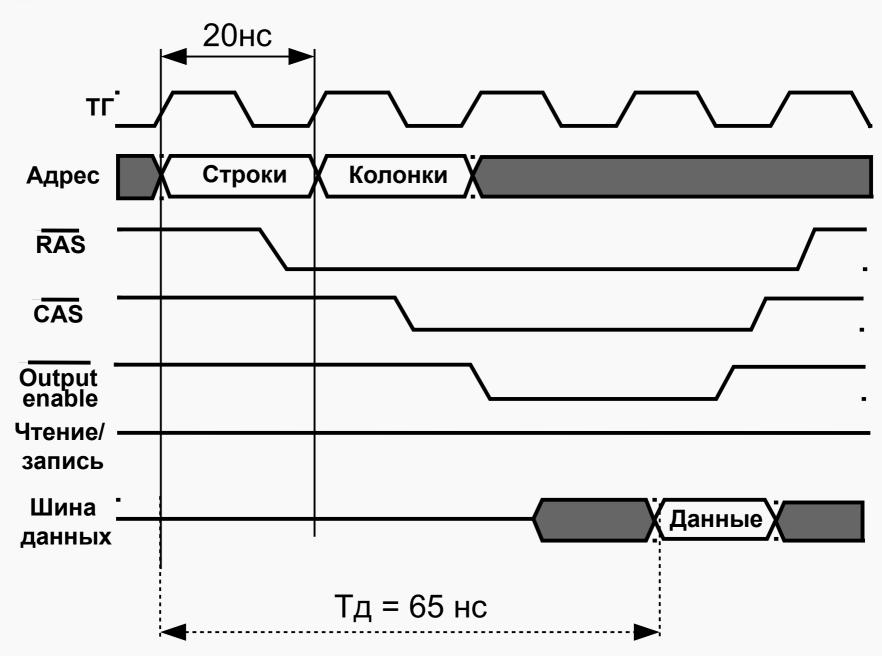

#### Синхронная память SDRAM

## Конструктивные особенности современной памяти

- Burst mode пакетный режим

- Double Data Rate передача данных и по фронту и по спаду

- SPD чип, содержащий идентификационную информацию

- Interleaving расслоение памяти, повышает производительность

- DDR4-2133 8192МВ **PC4-17000** индекс производительности

•

Поверхность 0

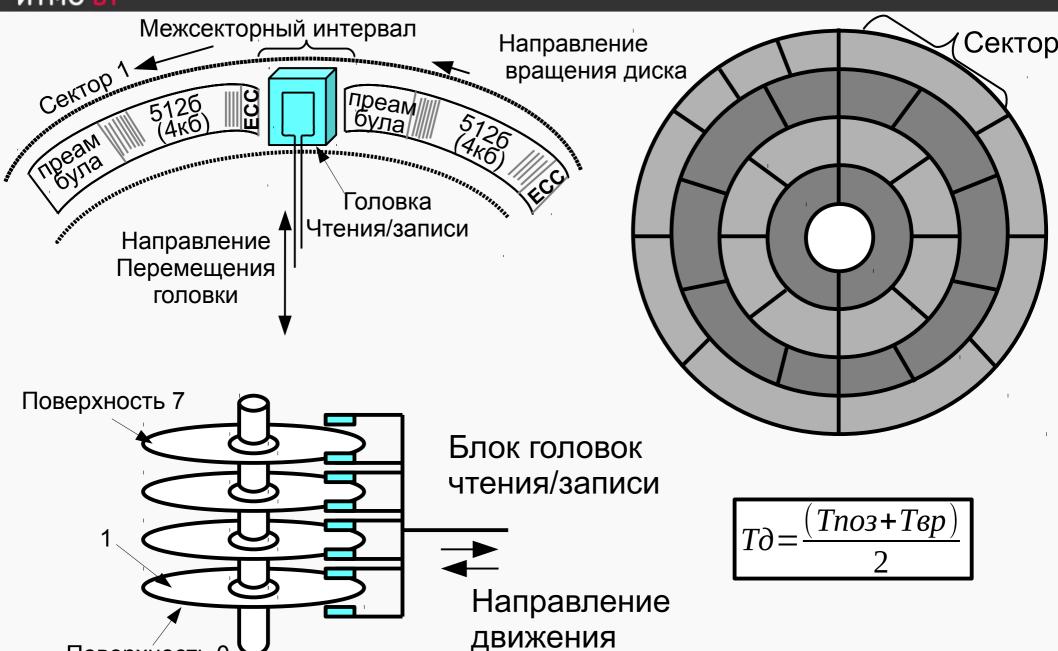

#### Память, ориентированная на записи

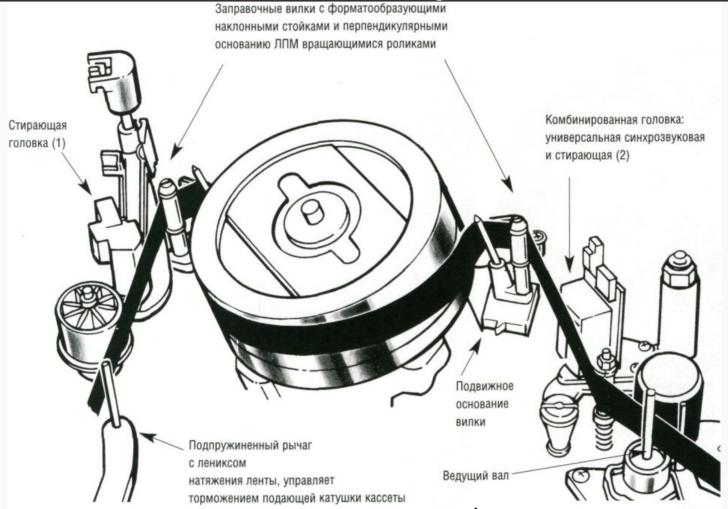

### Память, с последовательным доступом\*

\* на самом деле эта картинка от видемагнитофона, но принцип тот-же

Расположение дорожек

Лента

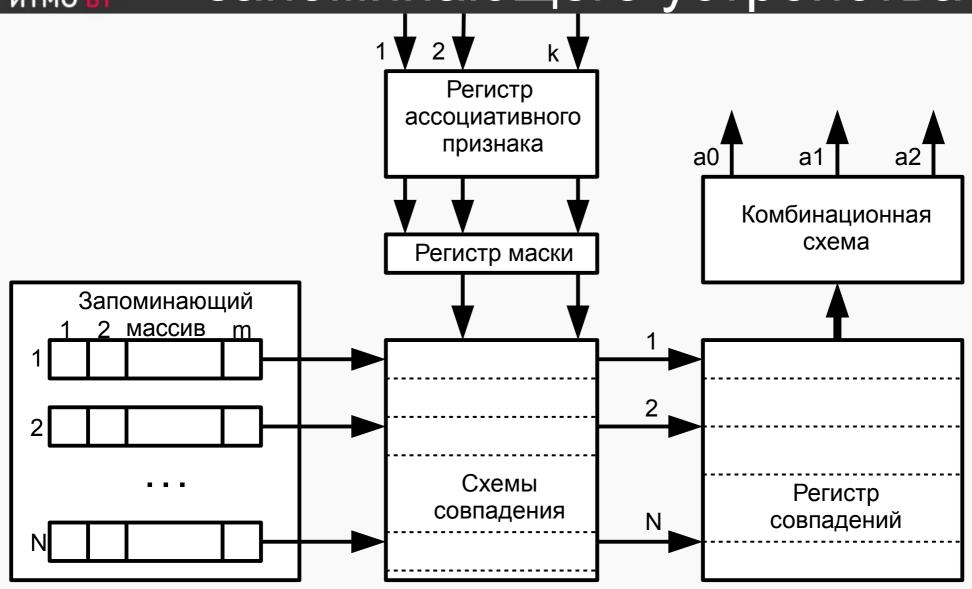

# Структура ассоциативного запоминающего устройства

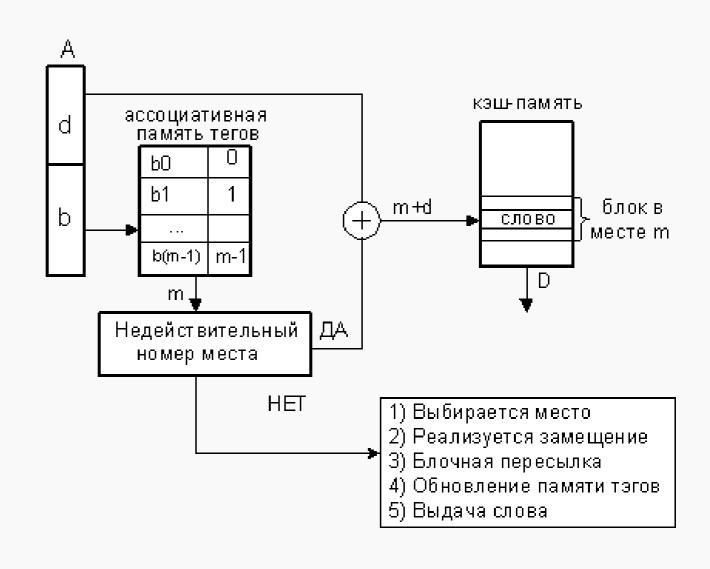

#### Кэш память

### Пирамида памяти

|                 | Объем               | Тд            | *           | Тип       | Управл.    |